# Intel® 413808 and 413812 SAS/SATA I/O Controllers

**Design Review Checklist**

May 2007

Order Number: 315046-003US

INFORMATION IN THIS DOCUMENT IS PROVIDED IN CONNECTION WITH INTEL® PRODUCTS. NO LICENSE, EXPRESS OR IMPLIED, BY ESTOPPEL OR OTHERWISE, TO ANY INTELLECTUAL PROPERTY RIGHTS IS GRANTED BY THIS DOCUMENT. EXCEPT AS PROVIDED IN INTEL'S TERMS AND CONDITIONS OF SALE FOR SUCH PRODUCTS, INTEL ASSUMES NO LIABILITY WHATSOEVER, AND INTEL DISCLAIMS ANY EXPRESS OR IMPLIED WARRANTY, RELATING TO SALE AND/OR USE OF INTEL PRODUCTS INCLUDING LIABILITY OR WARRANTIES RELATING TO FITNESS FOR A PARTICULAR PURPOSE, MERCHANTABILITY, OR INFRINGEMENT OF ANY PATENT, COPYRIGHT OR OTHER INTELLECTUAL PROPERTY RIGHT. Intel products are not intended for use in medical, life saving, life sustaining, critical control or safety systems, or in nuclear facility applications.

Intel may make changes to specifications and product descriptions at any time, without notice.

Intel Corporation may have patents or pending patent applications, trademarks, copyrights, or other intellectual property rights that relate to the presented subject matter. The furnishing of documents and other materials and information does not provide any license, express or implied, by estoppel or otherwise, to any such patents, trademarks, copyrights, or other intellectual property rights.

Designers must not rely on the absence or characteristics of any features or instructions marked "reserved" or "undefined." Intel reserves these for future definition and shall have no responsibility whatsoever for conflicts or incompatibilities arising from future changes to them.

Intel processor numbers are not a measure of performance. Processor numbers differentiate features within each processor family, not across different processor families. See <a href="http://www.intel.com/products/processor\_number">http://www.intel.com/products/processor\_number</a> for details.

The Val Vista may contain design defects or errors known as errata which may cause the product to deviate from published specifications. Current characterized errata are available on request.

Hyper-Threading Technology requires a computer system with an Intel<sup>®</sup> Pentium<sup>®</sup> 4 processor supporting Hyper-Threading Technology and an HT Technology enabled chipset, BIOS and operating system. Performance will vary depending on the specific hardware and software you use. See http://www.intel.com/info/hyperthreading/ for more information including details on which processors support HT Technology.

Contact your local Intel sales office or your distributor to obtain the latest specifications and before placing your product order.

Copies of documents which have an order number and are referenced in this document, or other Intel literature may be obtained by calling 1-800-548-4725 or by visiting Intel's website at http://www.intel.com.

AnyPoint, AppChoice, BoardWatch, BunnyPeople, CablePort, Celeron, Chips, CT Media, Dialogic, DM3, EtherExpress, ETOX, FlashFile, i386, i486, i960, iCOMP, InstantIP, Intel, Intel Centrino, Intel logo, Intel386, Intel486, Intel740, IntelDX2, IntelDX4, IntelSX2, Intel Create & Share, Intel GigaBlade, Intel InBusiness, Intel Inside, Intel Inside logo, Intel NetBurst, Intel NetMerge, Intel NetStructure, Intel Play, Intel Play logo, Intel SingleDriver, Intel SpeedStep, Intel StrataFlash, Intel TeamStation, Intel Xeon, Intel XScale, IPLink, Itanium, MCS, MMX, MMX logo, Optimizer logo, OverDrive, Paragon, PC Dads, PC Parents, PDCharm, Pentium, Pentium II Xeon, Pentium III Xeon, Performance at Your Command, RemoteExpress, SnartDie, Solutions960, Sound Mark, StorageExpress, The Computer Inside., The Journey Inside, TokenExpress, VoiceBrick, VTune, and Xircom are trademarks or registered trademarks of Intel Corporation or its subsidiaries in the United States and other countries.

May 2007

Order Number: 315046-003US

$^{st}$ Other names and brands may be claimed as the property of others.

Copyright © 2007, Intel Corporation. All Rights Reserved.

# **Contents**

May 2007 Order Number: 315046-003US

| 1.0                                       | Introduction                                                                                                                                                                                                                                                                                                                                                           | . 5                                    |

|-------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------|

| 2.0                                       | List of References                                                                                                                                                                                                                                                                                                                                                     | . 5                                    |

| 3.0                                       | Checklist Recommendations  3.1 Important Design and Debug Requirements 3.2 Termination Values Checklist 3.3 Reset Straps Checklist 3.4 Analog Filter Checklist 3.4.1 VCC1P2PLLS0, VCC1P2PLLS1 Filter Requirements 3.4.2 VCC1P2PLLP, VCC1P2PLLD Filter Requirements 3.4.3 VCC3P3LLX PLL Requirements 3.5 PCI Resistor Calibration 3.6 PCI Express Resistor Compensation | . 6<br>. 7<br>1 8<br>1 8<br>2 2<br>2 4 |

| Figure 1 2 3 4 5 6 7                      | VCC1P2PLLS0, VCC1P2PLLS1 Configuration                                                                                                                                                                                                                                                                                                                                 | 20<br>22<br>24<br>25<br>25             |

| Tab                                       | les                                                                                                                                                                                                                                                                                                                                                                    |                                        |

| 1<br>2<br>3<br>4<br>5<br>6<br>7<br>8<br>9 | List of References  Design and Debug Checklist  Termination Values Checklist  Reset Straps Checklist  PCI Express/PCI-X Strap Configuration Table  Required PLLs  VCC1P2PLLS0, VCC1P2PLLS1 Layout Guideline  VCC1P2PLLP, VCC1P2PLLD Layout Guideline  VCC3P3P3PLL Layout Guideline                                                                                     | . 6<br>. 7<br>1 7<br>1 8<br>1 9<br>2 1 |

# **Revision History**

| Date           | Revision | Description                     |

|----------------|----------|---------------------------------|

| October 2006   | 002      | Reformatted Variable attributes |

| September 2006 | 001      | Launch Release.                 |

#### Introduction 1.0

This document highlights design considerations the designer must review prior to manufacturing an adapter card or motherboard that implements the Intel $^{\otimes}$  413808 and 413812 SAS/SATA I/O Controllers (413808 and 413812).

The checklists address important connections to the 413808 and 413812 and any critical supporting circuitry. However, the checklists are only for reference; for complete design instructions, refer to the Intel® 413808 and 413812 SAS/SATA I/O Controllers Design Guide. These checklists are not necessarily complete and do not guarantee proper function of a design

Note:

This document is updated more frequently than the design guide and the latest terminations will supercede recommendations in the design guide.

#### 2.0 **List of References**

#### Table 1. **List of References**

| Document                                                                                      | Reference                                                          |

|-----------------------------------------------------------------------------------------------|--------------------------------------------------------------------|

| Intel® 81 348 I/O Processor Developer's Manual                                                | 315036                                                             |

| Intel® 413808 and 413812 SAS/SATA I/O Controllers<br>Datasheet                                | 315040                                                             |

| Intel® 413808 and 413812 SAS/SATA I/O Controllers<br>Design Guide                             | 315055                                                             |

| Intel $^{\circledR}$ 41 3808 and 41 3812 SAS/SATA I/O Controllers<br>Thermal Application Note | 315052                                                             |

| PCI Local Bus Specification, Revision 2.2                                                     | http://www.pcisig.com/specifications/conventional/conventional_pci |

| PCI-X Addendum to the PCI Local Bus Specification,<br>Revision 1.0a                           | http://www.pcisig.com/specifications/pcix_20                       |

| PCI Express Specification, Revision 1.0a                                                      | http://www.pcisig.com/specifications/pciexpress                    |

| PCI Express Base Specification 1.0a                                                           | http://www.pcisig.com/specifications/pciexpress                    |

| PCI Express Card Electromechanical Specification 1.0a                                         | http://www.pcisig.com/specifications/pciexpress                    |

Design Review Checklist Mav 2006 Order Number: 315046-003US

May 2006

Order Number: 315046-003US

Note:

#### **Checklist Recommendations** 3.0

The following tables provide the recommended pull-up and pull-down terminations for a 413808 and 413812 layout.

#### 3.1 **Important Design and Debug Requirements**

The following details are required for all 413808 and 413812 designs. Note that these tables are not an inclusive list. We recommend that the design guide is referenced for additional details.

Without implementing the debug requirements Intel is extremely limited in its ability to assist with debug issues involving the transport firmware and device driver.

#### Table 2. **Design and Debug Checklist**

| Paraman dations                                                                                                                                                                                  | C                                                                                                                                                                                                                                                               | Compliance |    |  |  |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------|----|--|--|

| Recommendations                                                                                                                                                                                  | Comments                                                                                                                                                                                                                                                        | Yes        | No |  |  |

| Debug Requirements                                                                                                                                                                               |                                                                                                                                                                                                                                                                 |            |    |  |  |

| The serial console port connector to the<br>UARTO port must be implemented to assist<br>in debug of Intel transport firmware.                                                                    | UARTO is dedicated as the debug port for the transport FW. This port is also implemented on Intel development boards. Without the UARTO port the debug of the transport firmware is extremely limited. Note: This port can be depopulated on production boards. |            |    |  |  |

| The JTAG port must be implemented on the<br>board to assist in debug of third party<br>device drivers.                                                                                           | A JTAG port provides the ability to connect a 3rd party debugger to the 413808 and 413812. Using a debugger is the only way to pinpoint potential device driver and transport firmware issues.  Notes:  1.                                                      |            |    |  |  |

|                                                                                                                                                                                                  | Design Notes                                                                                                                                                                                                                                                    |            |    |  |  |

| Supported and validated Flash components include Intel® StrataFlash® - 13, 13D and Intel® StrataFlash® Embedded Memory - P30.     A minimum size of 2 MB is required for the transport firmware. | For information on migrating from the J3-to-P30 refer to the following document:     http://developer.intel.com/design/flcomp/applnots/30666 7.htm  Note: Other CFI Flash memory may work but these components have not been validated.                         |            |    |  |  |

| Design Guide SAS routing<br>recommendations must be followed to<br>prevent compliance issues.                                                                                                    | It is important that the SAS lane lengths $<=5$ inches, routed as 100 ohms $+/-15\%$ differential signals with no more than two vias per signal.                                                                                                                |            |    |  |  |

| Separate the 1.2 V Core power from the SAS/SATA and PCIE planes.                                                                                                                                 | Separating the 1.2 V core supply minimizes noise coupling.                                                                                                                                                                                                      |            |    |  |  |

| The SAS PLL filtering must be connected to<br>ground. All the other PLL filters are not<br>connected ground.                                                                                     | Refer to Section 3.4.1 of this document                                                                                                                                                                                                                         |            |    |  |  |

| 1.2 V must be up before the 1.8 V. The     1.2 V must be down after the 1.8 V.                                                                                                                   | Refer to the power delivery chapter of the design guide for additional details.                                                                                                                                                                                 |            |    |  |  |

| JTAG TRST_N must be asserted at power-on                                                                                                                                                         | A reset supervisor to pulse <b>TRST_N</b> low on power-on and pull high after power-on. Refer to the JTAG section of the design guide.                                                                                                                          |            |    |  |  |

# 3.2 Termination Values Checklist

Table 3 lists these 413808 and 413812 termination values.

#### Table 3. Termination Values Checklist (Sheet 1 of 8)

| Signal                                | Recommendations                                                                                                                                                           | Comments                                                                                                     | Comp | liance |

|---------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------|------|--------|

| Signal                                | Resembled and the second                                                                                                                                                  | Comments                                                                                                     | Yes  | No     |

| S_TXP[7:0],<br>S_TXN[7:0]             | Connect each of S_TXP[7:0], S_TXN[7:0] lines with a 10 nF series capacitor with low ESR. Unused ports can be left unconnected.                                            | Storage Transmit: carries the differential output serial data and embedded clock for the SAS/SATA interface. |      |        |

| S_RXP[7:0],<br>S_RXN[7:0]             | Connect each of S_RXP[7:0], S_RXN[7:0] lines with a 10 nF series capacitor with low ESR.  Unused ports can be left unconnected.                                           | Storage Receive: carries the differential input serial data and embedded clock for the SAS/SATA interface.   |      |        |

| S_CLKNO, S_CLKPO                      | <ul> <li>connect to differential 125 MHz ±100 ppm or a 150 MHz ±100 ppm oscillator.</li> <li>use a 0.1 μF AC coupling series capacitor on S_CLKNO and S_CLKPO.</li> </ul> | Differential storage clock                                                                                   |      |        |

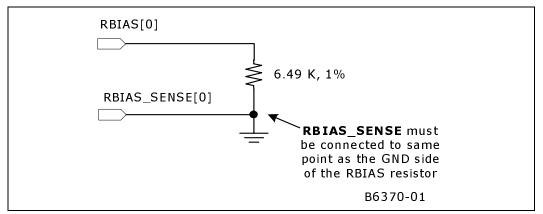

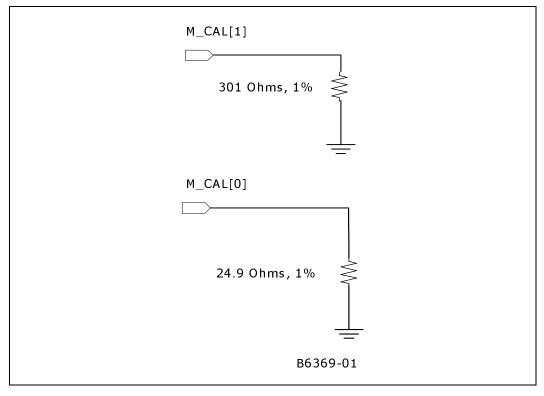

| RBIAS[1:0]                            | 6.49 KΩ 1% to <b>GND</b> . Refer to Figure 7.                                                                                                                             |                                                                                                              |      |        |

| RBIAS_SENSE[1:0]                      | Connect to the same GND point of<br>the RBIAS[1:0] resistors. Refer<br>to Figure 7.                                                                                       |                                                                                                              |      |        |

| S_ACTO/SCLOCKO,<br>S_STATO/SLOADO     | NC when not used.     SGPIO[0] is disabled: Connect to LED with series resistor to indicate activity and status for storage engine[0].                                    |                                                                                                              |      |        |

| S_ACT1,<br>S_STAT1                    | NC when not used.     SGPIO[0] is disabled: These signals can be connected to an LED with series resistor to indicate activity and status for storage engine[1].          |                                                                                                              |      |        |

| S_ACT2/SDATAINO,<br>S_STAT2/SDATAOUT0 | NC when not used.     SGPIO[0] is disabled: These signals can be connected to an LED with series resistor to indicate activity or status for storage engine[2].           |                                                                                                              |      |        |

| S_ACT3,<br>S_STAT3                    | NC when not used.     SGPIO[0] is disabled: These signals can be connected to an LED with series resistor to indicate activity and status for storage engine[3].          |                                                                                                              |      |        |

| S_ACT4/SCLOCK1,<br>S_STAT4/SLOAD1     | NC when not used.     SGPIO[1] is disabled: These signals can be connected to an LED with series resistor to indicate activity/status for storage engine[4].              |                                                                                                              |      |        |

Intel® 413808 and 413812 I/O Controllers

May 2006

Order Number: 315046-003US

Intel® 413808 and 413812 I/O Controllers

Design Review Checklist

Table 3. Termination Values Checklist (Sheet 2 of 8)

| Signal                                    | Recommendations                                                                                                                                                                                                                                                                                                                                        | Comments                                                                            | Comp | liance |

|-------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------|------|--------|

| Signal                                    | Recommendations                                                                                                                                                                                                                                                                                                                                        |                                                                                     | Yes  | No     |

| S_ACT5,<br>S_STAT5                        | NC when not used.     SGPIO[1] is disabled: These signals can be connected to an LED with series resistor to indicate activity /status for storage engine[5].                                                                                                                                                                                          |                                                                                     |      |        |

| S_ACT6/SDATAIN1,<br>S_STAT6/<br>SDATAOUT1 | NC when not used. SGPIO[1] is disabled: These signals can be connected to an LED with series resistor to indicate activity/status for storage engine[6].                                                                                                                                                                                               |                                                                                     |      |        |

| S_ACT7/,<br>S_STAT7                       | NC when not used.     SGPIO[1] is disabled: These signals can be connected to an LED with series resistor to indicate activity/status for storage engine[7].                                                                                                                                                                                           |                                                                                     |      |        |

| REFCLKP,<br>REFCLKN                       | For PCI Express interface: connect to a 100 MHz oscillator.  PCI-X end point: connect the REFCLKP to a resistor divider such that the REFCLKP node is connected to both a 17.4 K to VCC3P3 and a 4.7 K connected to GND. REFCLKN must be connected to GND.                                                                                             | <b>Note:</b> 100 MHz oscillator is required for the PCI Express differential clock. |      |        |

| PETP[7:0],<br>PETN[7:0]                   | Series capacitors with value of<br>75 nF to 200 nF (low ESR) on each<br>of the lines.                                                                                                                                                                                                                                                                  |                                                                                     |      |        |

| PERP[7:0],<br>PERN[7:0]                   | No series capacitor needed.     NC when not used.                                                                                                                                                                                                                                                                                                      |                                                                                     |      |        |

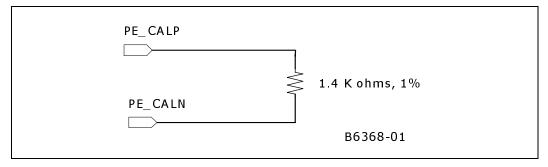

| PE_CALP,<br>PE_CALN                       | 1.4 KΩ 1% resistor is connected<br>between the PE_CALP and<br>PE_CALN.                                                                                                                                                                                                                                                                                 |                                                                                     |      |        |

| P_AD[63:32],<br>P_CBE[7:4]#,<br>P_PAR64   | <ul> <li>When only PCI Express interface active, these signals are internally pulled-up and can be left as NC.</li> <li>When the PCIX_PULLUP# is enabled (pulled to 0), these signals are internally pulled-up.</li> <li>When the PCIX_32BIT# is enabled (32-bit bus width), these signals are internally pulled-up and can be left as NCs.</li> </ul> |                                                                                     |      |        |

| P_AD[31:0],<br>P_CBE[3:0]#                | <ul> <li>When only PCI Express interface<br/>active these signals are internally<br/>pulled-up and can be left as NC.</li> </ul>                                                                                                                                                                                                                       |                                                                                     |      |        |

| P_REQ#                                    | PCI Express: P_GNT[0]# / P_REQ# has an internal pull-up and can be left as a NC. PCI Endpoint mode (external arbiter) PCIX_EP# = 0: This is the output request signal for the ATU and needs to connect to the external arbiter's P_REQ# lines.                                                                                                         |                                                                                     |      |        |

Table 3. Termination Values Checklist (Sheet 3 of 8)

| Signal                                                     | Recommendations                                                                                                                                                                                                                                                                                                                              | Comments                                                                                               | Comp | liance |

|------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------|------|--------|

| Signal                                                     | Recommendations                                                                                                                                                                                                                                                                                                                              | Comments                                                                                               | Yes  | No     |

| P_GNT#                                                     | <ul> <li>PCI Express: P_REQ[0]# / P_GNT# has an internal pull-up and can be left as a NC.</li> <li>PCI Endpoint mode (external arbiter): P_GNT# is input grant signal for the ATU. This pin should be pulled up to VCC3P3 with an 8.2 KΩ resistor.</li> </ul>                                                                                |                                                                                                        |      |        |

| P_REQ64#                                                   | <ul> <li>When only PCI Express interface is active, these signals are internally pulled-up and can be left as a NC.</li> <li>When the PCIX_PULLUP# is enabled (pulled to 0), this signal is internally pulled-up.</li> <li>PCI endpoint mode the width of the bus is indicated by the state of REQ64# at the rising edge of RST#.</li> </ul> |                                                                                                        |      |        |

| P_ACK64#,<br>P_PAR,<br>P_SERR#,<br>P_PERR#,<br>P_INT[D:A]# | When only PCI Express interface is active these signals are internally pulled-up and can be left as a NC. When the PCIX_PULLUP# is enabled (pulled to 0), these signals are internally pulled-up.                                                                                                                                            |                                                                                                        |      |        |

| P_FRAME#,<br>P_IRDY#,<br>P_TRDY#,<br>P_STOP#,<br>P_DEVSEL# | When only PCI Express interface is active these signals are internally pulled-up and can be left as a NC. When the PCIX_PULLUP# is enabled (pulled to 0), these signals are internally pulled-up. PCI endpoint mode the state of these signals are used as for PCI-X initialization pattern at the rising edge of RST#.                      | Refer to the <i>PCI-X Specification 1.0b</i> for more information on the PCI-X Initialization pattern. |      |        |

| P_M66EN                                                    | <ul> <li>PCI Express: P_M66EN has an internal pull-up and can be left as a NC.</li> <li>PCI Endpoint mode PCIX_EP# = 0: Refer to Section 3.1 of the Design Guide.</li> </ul>                                                                                                                                                                 |                                                                                                        |      |        |

| P_IDSEL                                                    | PCI Express: P_IDSEL has an internal pull-up and can be left as a NC. PCI Endpoint mode PCIX_EP# = 0: Connect to AD lines Section 3.1.2 of the Design Guide.                                                                                                                                                                                 |                                                                                                        |      |        |

| P_CLKIN                                                    | For PCI Express only this signal should be connected to GND.     PCI Endpoint mode (PCIX_EP# = 0): connect to the system PCI clock.                                                                                                                                                                                                          |                                                                                                        |      |        |

| P_PCIXCAP                                                  | GND this pin.                                                                                                                                                                                                                                                                                                                                |                                                                                                        |      |        |

| P_BMI                                                      | <ul> <li>When PCI Express only: this signal can be left as a no connect.</li> <li>For PCI-X: no connect when not used.</li> </ul>                                                                                                                                                                                                            |                                                                                                        |      |        |

May 2006 Intel® 413808 and 413812 I/O Controllers

Order Number: 315046-003US

Order Number: 9

# Table 3. Termination Values Checklist (Sheet 4 of 8)

| Signal                       | Recommendations                                                                                                                                                                                                                 | Comments                                                                                                                                                                                                             | Comp | liance |

|------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|--------|

| Signal                       | Recommendations                                                                                                                                                                                                                 | Comments                                                                                                                                                                                                             | Yes  | No     |

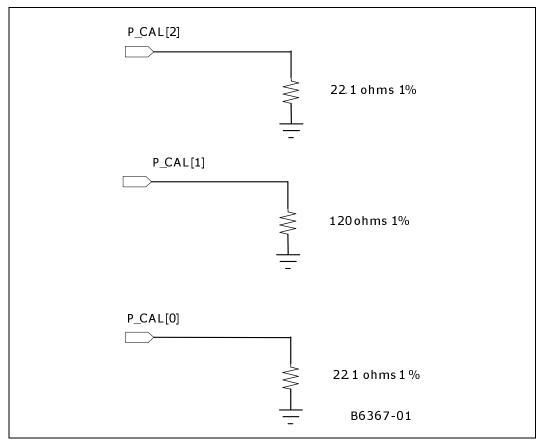

| P_CAL[0], P_CAL[2]           | <ul> <li>When PCI-X interface is used: This pin is connected to a separate 22.1 Ω1% resistor to GND. See Section 3.5 for more information.</li> <li>When PCI-X interface is not used: These pins can be left as NCs.</li> </ul> | PCI Calibration: is connected to an external calibration resistor to dynamically adjust their slew rate and drive strength to compensate for voltage and temperature variations.                                     |      |        |

| P_CAL[1]                     | <ul> <li>When PCI-X is used: This pin is connected to a separate 121 Ω 1% resistor to GND. See Section 3.5 for more information.</li> <li>When PCI-X interface is not used: These pins can be left as NCs.</li> </ul>           |                                                                                                                                                                                                                      |      |        |

| PE_CALP<br>PE_CALN           | Connect <b>PE_CALP</b> ball through 1.4 K 1% resistor to the <b>PE_CALN</b> ball. Refer to Figure 5.                                                                                                                            | Note: this is required even when the PCI-Express interface is not used.                                                                                                                                              |      |        |

| A[24:0], POE#,<br>PB_RSTOUT# | Unused pins can be left unconnected. Refer to Design guide for PBI bus connection recommendations.                                                                                                                              |                                                                                                                                                                                                                      |      |        |

| D[15:0], PCE[1:0]#,<br>PWE#  | These are also used for reset straps refer to the Reset Strap Table 3.3. Refer to Design guide for PBI bus connection recommendations.                                                                                          |                                                                                                                                                                                                                      |      |        |

| HS_ENUM#                     | Can be left unconnected when<br>Hot-Swap not used                                                                                                                                                                               |                                                                                                                                                                                                                      |      |        |

| HS_LSTAT                     | When Compact PCI Hot-Swap is not supported, this signal must be tied to GND.                                                                                                                                                    | Hot-Swap Latch Status: An input indicating the state of the ejector switch.  0 = Indicates the ejector switch is closed.  1 = Indicates the ejector switch is open.  0 = Connect to GND.  1 = 8.2 KΩ pull-up to VCC. | _    |        |

| HS_LED_OUT                   | Connect to Hot-Swap blue LED.     When CompactPCI* Hot-Swap is not supported this signal can be left unconnected.                                                                                                               |                                                                                                                                                                                                                      |      |        |

Table 3. Termination Values Checklist (Sheet 5 of 8)

| Signal                                            | Recommendations                                                                                                                                                                                                                                                                                                                                     | Comments                                                                                                                                                                                                                                                                                                                                                                                                                                      | Comp | liance |

|---------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|--------|

| Signal                                            | Recommendations                                                                                                                                                                                                                                                                                                                                     | Comments                                                                                                                                                                                                                                                                                                                                                                                                                                      | Yes  | No     |

| HS_FREQ[1:0] /<br>CR_FREQ[1:0]                    | See comments                                                                                                                                                                                                                                                                                                                                        | Hot-Swap Frequency: While in Hot-Swap mode, (these are only valid when PCIX_EP# = 0 and HS_SM# = 0).  00 = 133 MHz PCI-X.  01 = 100 MHz PCI-X.  10 = 66 MHz PCI-X.  11 = 33 or 66 MHz. PCI (frequency depends on P_M66EN).  Central Resource Frequency: While in Central Resource mode (these are only valid when PCIX_EP# = 1).  00 = 133 MHz.  01 = 100 MHz.  10 = 66 MHz.  11 = 33 MHz.  Note:  0 = connect to GND.  1 = internal pull-up. |      |        |

| P_INT[D:A]# /<br>XINT[3:0]#/<br>GPIO[11:8]        | <ul> <li>When using as interrupts and PCIX_EP# = 0: Act as outputs no termination is required</li> <li>When using as interrupts and PCIX_EP# = 1: 8.2 KΩ pull-up required on each line</li> <li>When using as GPIOs: 8.2 KΩ pull-up required on each line</li> </ul>                                                                                | When INTERFACE_SEL_PCIX# = 0: PCI Interrupt: These outputs are level sensitive. When INTERFACE_SEL_PCIX# = 1: External Interrupt: requests are used by external devices to request interrupt service. These pins are level-detect inputs and are internally synchronized. These pins go to the XINT[3:0]# inputs of the Interrupt Controller.                                                                                                 |      |        |

| HPI#,<br>NMIO#,<br>NMI1#,<br>XINT[7:4]#           | 8.2 KΩ pull-ups                                                                                                                                                                                                                                                                                                                                     |                                                                                                                                                                                                                                                                                                                                                                                                                                               |      |        |

| GPIO[7:0] /<br>XINT[15:8]# /<br>CHAPOUT           | 8.2 KΩ pu  -ups                                                                                                                                                                                                                                                                                                                                     | <ul> <li>General Purpose I/O (default mode).</li> <li>External Interrupt: These pins are level-detects and are internally synchronized.</li> <li>CHAPOUT: GPIO[7] When enabled it will override the normal GPIO[7] function.</li> </ul>                                                                                                                                                                                                       |      |        |

| SCLO,<br>SDAO,<br>SCL1,<br>SDA1,<br>SCL2,<br>SDA2 | When used external pull-up to VCC is required. Refer to the I <sup>2</sup> C specification for information on calculating the pull-up.  Note: I <sup>2</sup> C port 0 can only used for SEP enclosure management.  Note: I <sup>2</sup> C port 1 and port 2 are not available on 413808 and 413812 and must have pull-ups.  2K pull-up when unused. | The pull-up value is dependent on the bus loading. Refer to the I <sup>2</sup> C specification http://www.semiconductors.philips.com/acrobat/literature/9398/39340011.pdf                                                                                                                                                                                                                                                                     |      |        |

May 2006 Intel® 413808 and 413812 I/O Controllers

Order Number: 315046-003US

Intel® 413808 and 413812 I/O Controllers

Design Review Checklist

Table 3. Termination Values Checklist (Sheet 6 of 8)

| Signal                                    | Recommendations                                                                                                                                                                                                                                                                                                                                                                                                                                       | Comments                                                                                                                                                                                                                                                                                                        | Comp | liance |

|-------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|--------|

| Signal                                    | Recommendations                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                                                                                                                                                                                                                                                                                                 | Yes  | No     |

| SMBCLK                                    | <ul> <li>For PCI Express adapter cards:         <ul> <li>When the SMBus is used, there should be isolation device such as the LTC4301 between this signal and PE_SMCK on the PCI Express connector.</li> </ul> </li> <li>For PCI Express motherboard applications:         <ul> <li>When SMBus is used a pull-up is required (value is dependent on the loading).</li> <li>When SMBus is unused, a 8.2 KΩ pull-up is required.</li> </ul> </li> </ul> | LTC4301 is a hot-swappable 2-wire bus buffer that allows card insertion without corruption of the data and clock buses. Refer to the Linear Technology website http://www.linear.com/pc/productDe tail.do?navId=H0,C1,C1007,C1070,P 2460.  Refer also to the http://www.smbus.org for the latest specification. |      |        |

| SMBDAT                                    | For PCI Express adapter cards:  When the SMBus is used, there should be isolation device such as the LTC4301 between this signal and PE_SMDAT on the PCI Express connector.  For PCI Express motherboard applications:  When SMBus is used a pull-up is required (value is dependent on the loading).  When SMBus is unused, a 8.2 KΩ pull-up is required.                                                                                            | LTC4301 is a hot-swappable 2-wire bus buffer that allows card insertion without corruption of the data and clock buses. Refer to the Linear Technology website http://www.linear.com/pc/productDe tail.do?navId=H0,C1,C1007,C1070,P2460.  Refer also to the http://www.smbus.org for the latest specification.  |      |        |

| U0_RXD,<br>U1_RXD                         | The serial console port connector to the UARTO port must be implemented to assist in debug of Intel transport firmware.  When unused, connect to GND.  UART 1 is not available for 413808 and 413812.                                                                                                                                                                                                                                                 | Note: UARTO is dedicated as the debug port for the transport firmware as implemented on Intel development boards.                                                                                                                                                                                               |      |        |

| U0_TXD,<br>U0_RTS#,<br>U1_TXD,<br>U1_RTS# | The serial console port connector to the UARTO port must be implemented to assist in debug of Intel transport firmware.  Can be left unconnected when unused.  UART1 is not available for 413808 and 413812.                                                                                                                                                                                                                                          | Note: UARTO is dedicated as the debug port for the transport firmware as implemented on Intel development boards.                                                                                                                                                                                               |      |        |

| U0_CTS#,<br>U1_CTS#                       | <ul> <li>The serial console port connector to the UARTO port must be implemented to assist in debug of Intel transport firmware.</li> <li>When unused, 8.2 KΩ pull-up.</li> <li>UART1 is not available for 413808 and 413812.</li> </ul>                                                                                                                                                                                                              | Note: UARTO is dedicated as the debug port for the transport firmware as implemented on Intel development boards.                                                                                                                                                                                               |      |        |

| тск                                       | The JTAG port must be implemented on the board to assist in debug of third party device drivers.  8.2K pull-up when used. Refer to the JTAG chapter.  GND when unused.                                                                                                                                                                                                                                                                                | Test Clock: Provides clock input for IEEE 1149.1 Boundary Scan Testing (JTAG).                                                                                                                                                                                                                                  |      |        |

Table 3. Termination Values Checklist (Sheet 7 of 8)

| Si amal   | Recommendations                                                                                                                                                                                                                                                                          | Comments                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | Comp | liance |

|-----------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|--------|

| Signal    | Recommendations                                                                                                                                                                                                                                                                          | Comments                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | Yes  | No     |

| TDI       | The JTAG port must be implemented on the board to assist in debug.  8.2K pull-up when used. Refer to the JTAG chapter.  NC when unused has weak pull-up.                                                                                                                                 | Test Data Input: The JTAG serial input pin.                                                                                                                                                                                                                                                                                                                                                                                                                                                 |      |        |

| TDO       | The JTAG port must be implemented on the board to assist in debug. When used refer to the JTAG chapter. NC when unused.                                                                                                                                                                  | <b>Test Data Output:</b> The serial output pin for the JTAG feature.                                                                                                                                                                                                                                                                                                                                                                                                                        |      |        |

| TRST#     | The JTAG port must be implemented on the board to assist in debug. When used refer to the JTAG chapter. GND when unused.                                                                                                                                                                 | Test Reset: This pin has a weak internal pull-up.                                                                                                                                                                                                                                                                                                                                                                                                                                           |      |        |

| TMS       | The JTAG port must be implemented on the board to assist in debug.  8.2 K pull-up when used. Refer to the JTAG chapter.  NC when unused has weak pull-up.                                                                                                                                | Test Mode Select: This pin has a weak internal pull-up.                                                                                                                                                                                                                                                                                                                                                                                                                                     |      |        |

| WARM_RST# | When PCI-X interface is used: 1 K pull-up. When PCI-Express used: This pin is used when the sticky bit functionality is required. In this scenario, the WARM_RST# pin must be tied to the system reset PCI_RST# signal while the P_RST# pin can be tied to the system power good signal. | Warm Reset is the same as a cold reset, except sticky configuration bits are not reset.  Notes:  - When the PCI Express interface is used as an endpoint, the PCI Express in-band Hot Reset Mechanism can also be used to provide the sticky bit functionality.  - On the customer reference board, WARM_RST# is tied to the SRST_N to provide a JTAG debugger reset.  - Driving WARM_RST# using any other methods than suggested above may result in unpredictable behavior of the device. |      |        |

| NC        | No Connect: pins have no usable function and must not be connected to any signal, power or ground.                                                                                                                                                                                       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |      |        |

| THERMDA   | Connect to the anode of the thermal diode.  NC when unused.                                                                                                                                                                                                                              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |      |        |

May 2006 Intel® 413808 and 413812 I/O Controllers

Order Number: 315046-003US

Intel® 413808 and 413812 I/O Controllers

Design Review Checklist

## Table 3. Termination Values Checklist (Sheet 8 of 8)

| Signal  | Recommendations                                                                                | Comments | Compliance |    |

|---------|------------------------------------------------------------------------------------------------|----------|------------|----|

| Signal  |                                                                                                | Comments | Yes        | No |

| THERMDC | Connect to the cathode of the thermal diode.  NC when unused.                                  |          |            |    |

| PUR1    | This pin must be pulled up to VCC3P3 with an external 8.2 KΩ 5% resistor for proper operation. |          |            |    |

| VCCVIO  | For PCI-Express interface: connect to ground. For PCI-X interface: Connect to 3.3 V.           |          |            |    |

# 3.3 Reset Straps Checklist

Table 4 provides a list of reset straps that are multiplexed on the Peripheral Address Bus **A[24:0]**. These pins are latched on the rising edge of **P\_RST#**. All reset strap signals are internally pulled to logic 1 by default. An external 4.7 K $\Omega$  5% pull-down resistor is required to force a logic 0 on these pins.

Table 4. Reset Straps Checklist (Sheet 1 of 2)

| Signal                                  | Recommendations                                                                                                                                                                                                         | Comments                                                                                                                                                                                                                                                                                                                                                                                                                                               | Compliance |    |

|-----------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------|----|

|                                         | Recommendations                                                                                                                                                                                                         | Comments                                                                                                                                                                                                                                                                                                                                                                                                                                               | Yes        | No |

| BOOT_WIDTH_8#                           | 0 = 8 bits wide, 0 = 4.7 KΩ resistor<br>pull down.<br>1 = 16 bits wide (Default mode<br>internal pull-up).                                                                                                              | Note: Muxed onto signal A[0].                                                                                                                                                                                                                                                                                                                                                                                                                          |            |    |

| CFG_CYCLE_EN#                           | $\begin{array}{ll} 0 = & \text{Configuration Cycles enabled, 0} \\ = & 4.7 \ K\Omega \ \text{resistor pull down.} \\ 1 = & \text{Configuration Retry enabled} \\ & \text{(Default mode internal pull-up).} \end{array}$ | Note: Muxed onto signal A[1].                                                                                                                                                                                                                                                                                                                                                                                                                          |            |    |

| HOLD_X0_IN_RST#                         | 0 = Hold Scale in reset, 0 = 4.7 KΩ resistor pull down. 1 = Do not hold in reset (Default mode internal pull-up).                                                                                                       | Note: Muxed onto signal A[2].                                                                                                                                                                                                                                                                                                                                                                                                                          |            |    |

| HOLD_X1_IN_RST#                         | 0 = Hold in reset, 0 = 4.7 KΩ resistor pull down. 1 = Do not hold in reset (Default mode internal pull-up).                                                                                                             | Note: Muxed onto signal A[3].                                                                                                                                                                                                                                                                                                                                                                                                                          |            |    |

| EXT_ARB#                                | Requires a 4.7 K ohms resistor pull down.                                                                                                                                                                               | Note: Muxed onto signal A[6]. Note: This signal must always be pulled down.                                                                                                                                                                                                                                                                                                                                                                            |            |    |

| INTERFACE_SEL_PCIX#                     | For PCI Express - No connect. For PCI-X - Requires a 4.7K ohms resistor pull down.                                                                                                                                      | Interface Select PCI-X: determines which ATU is function 0 . $0 = 4.7 \text{ K}\Omega$ resistor pull down . $1 = \text{internal pull up}$ . Note: Muxed onto signal A[10].                                                                                                                                                                                                                                                                             |            |    |

| PCIX_EP#                                | For PCI-X endpoint: <b>Requires a</b> 4.7 KΩ resistor pull down.                                                                                                                                                        | 413808 and 413812 operates as in PCI-X End Point mode.  Note: muxed onto signal A[11].                                                                                                                                                                                                                                                                                                                                                                 |            |    |

| PCIE_RC#                                | No connect.                                                                                                                                                                                                             | 413808 and 413812 operates as in endpoint mode only (default with internal pull-up).  Note: muxed onto signal A[12].                                                                                                                                                                                                                                                                                                                                   |            |    |

| SMB_A5,<br>SMB_A3,<br>SMB_A2,<br>SMB_A1 | Refer to comments.                                                                                                                                                                                                      | SM Bus Address: maps to address bits 5, 3, 2, and 1 where bits[7:0] represent the address the SMBus slave port will respond to when access is attempted.  0 = address bit will be low. 1 = address bit will be high (Default mode).  Note: SMB_A5 muxed onto signal A[16].  Note: SMB_A3 muxed onto signal A[15].  Note: SMB_A2 muxed onto signal A[14].  Note: SMB_A1 muxed onto signal A[13].  0 = 4.7 KΩ resistor pull down.  1 = internal pull up. |            |    |

| PCIX_PULLUP#                            | When pulled-low enables the following signal pull-ups: P_AD[63:32], P_C/BE[7:4]#, P_PAR64, P_REQ64#, P_ACK64#, P_FRAME#, P_IRDY#, P_TRDY#, P_STOP#, P_DEVSEL#, P_SERR#, P_PERR#, P_INT[D:A]#                            | PCI-X Pull Up:  0 = enable PCI pull up resistors.  1 = disable PCI pull up resistors (Default mode).  Note: Muxed onto signal A[17].  0 = 4.7 KΩ resistor pull down.  1 = internal pull up.                                                                                                                                                                                                                                                            |            |    |

May 2006 Order Number: 315046-003US Intel® 413808 and 413812 I/O Controllers

Design Review Checklist

15

Table 4. Reset Straps Checklist (Sheet 2 of 2)

| Signal.           | D de ti                                                                                                                              | C                                                                                                                                                                                                                                                                                                                         | Compliance |    |

|-------------------|--------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------|----|

| Signal            | Recommendations                                                                                                                      | Comments                                                                                                                                                                                                                                                                                                                  | Yes        | No |

| PCIX_32BIT#       | When 32 PCI-X bus enabled the following signals have internal pull-ups: P_AD[63:32], P_C/BE[7:4]# and P_PAR64 and can be left as NC. | 32-Bit PCI-X Bus:  0 = 32 bit wide PCI-X bus.  1 = 64 bit wide PCI-X bus. (Default mode).  Note: Muxed onto signal A[18].  0 = 4.7 KΩ resistor pull down.  1 = internal pull up.                                                                                                                                          |            |    |

| PCIXM1_100#       | Refer to comments.                                                                                                                   | PCI-X Mode 1 100 MHz Enable: $0 = \text{limit PCI-X mode 1 to 100 MHz}$ $1 = 133 \text{ MHz enabled (Default mode)}$ Note: Muxed onto signal A[19]. $0 = 4.7 \text{ K}\Omega$ resistor pull down. $1 = \text{internal pull up.}$                                                                                          |            |    |

| HS_SM#            | Refer to comments.                                                                                                                   | Hot-Swap Startup Mode:  0 = Hot-Swap mode enabled.  1 = Hot-Swap mode disabled (Default mode).  Note: Muxed onto signal A[21]  0 = 4.7 KΩ resistor pull down.  1 = internal pull up.                                                                                                                                      |            |    |

| FW_TIMER_OFF#     | Refer to comments.                                                                                                                   | Firmware Timer Off:  0 = firmware timer disabled.  1 = firmware timer enabled (Default mode).  Note: Muxed onto signal A[22]  0 = 4.7 KΩ resistor pull down.  1 = internal pull up.                                                                                                                                       |            |    |

| CONTROLLER_ONLY#  | 4.7 K $\Omega$ resistor pull down.                                                                                                   | Controller-Only Enable:  0 = Controller only, RAID disabled.  1 = RAID enabled (default mode) this is not supported in 413808 and 413812.  NOTE: Muxed onto signal A[23].                                                                                                                                                 |            |    |

| DF_SEL[2:0]       | 413808 and 413812 configurations:  • Single-core 8-port DF_SEL[2:0] = 000.  • Dual-core 8-port DF_SEL[2:0] = 100.                    | DF_SEL[2:0] configurations set as follows: 0 = 4.7 KΩ resistor pull down. 1 = internal pull up and can be <b>NC</b> .                                                                                                                                                                                                     |            |    |

| CLK_SRC_PCIE#     | Refer to comments.                                                                                                                   | Clock Source PCI-E: selects the PCI Express Refclk pair as the input clock to the PLLs that control most internal logic.  0 = source clock is REFCLKP/REFCLKN.  1 = source clock comes from the active PCI interface (Default mode).  Note: Muxed onto signal PWE#  0 = 4.7 KΩ resistor pull down.  1 = internal pull up. |            |    |

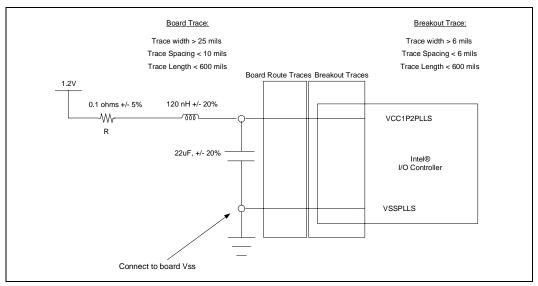

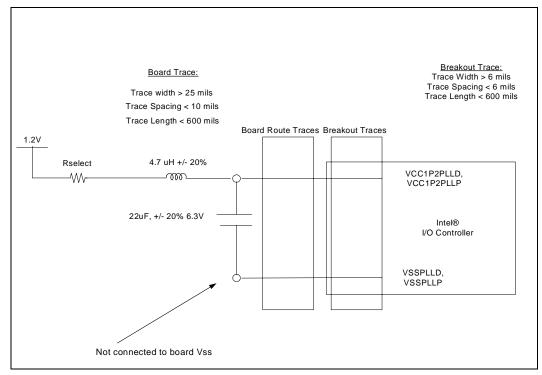

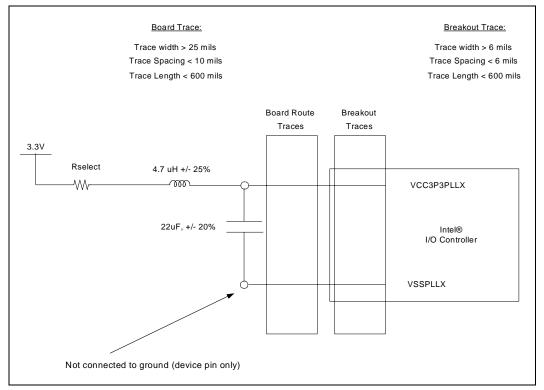

| LK_DN_RST_BYPASS# | Use for PCI Express mode.                                                                                                            | Link Down Reset Bypass: Disables the full chip reset that would normally be caused by a Link Down or hot reset.  0 = Do not reset on Link Down.  1 = Reset on Link Down (default mode).  Muxed onto signal A[24]                                                                                                          |            |    |