# VRM 9.1 DC-DC Converter Design Guidelines

Order Number 298646-001

January 2002

Information in this document is provided in connection with Intel<sup>®</sup> products. No license, express or implied, by estoppel or otherwise, to any intellectual property rights is granted by this document. Except as provided in Intel's Terms and Conditions of Sale for such products, Intel assumes no liability whatsoever, and Intel disclaims any express or implied warranty, relating to sale and/or use of Intel<sup>®</sup> products including liability or warranties relating to fitness for a particular purpose, merchantability, or infringement of any patent, copyright or other intellectual property right. Intel products are not intended for use in medical, life saving, or life sustaining applications.

Intel may make changes to specifications and product descriptions at any time, without notice.

Designers must not rely on the absence or characteristics of any features or instructions marked "reserved" or "undefined." Intel reserves these for future definition and shall have no responsibility whatsoever for conflicts or incompatibilities arising from future changes to them.

This document contains information on products in the design phase of development. Do not finalize a design with this information. Revised information will be published when the product is available. Verify with your local sales office that you have the latest datasheet before finalizing a design.

Intel processors may contain design defects or errors known as errata, which may cause the product to deviate from published specifications. Current characterized errata are available on request.

Copyright © Intel Corporation 2001, 2002.

Intel, Pentium, and Xeon are trademarks or registered trademarks of Intel Corporation or its subsidiaries in the United States and other countries.

\*Other names and brands may be claimed as the property of others.

## Table Of Contents

| 1 | Ele  | ectrical Specifications5          |

|---|------|-----------------------------------|

|   | 1.1  | Output Requirements5              |

|   | 1.2  | Input Voltage and Current         |

|   | 1.3  | Control Inputs10                  |

|   | 1.4  | Remote Sense (VO-sen+, VO-sen-)11 |

|   | 1.5  | Power Good Output (PWRGD)11       |

|   | 1.6  | VRM Present (VRM-pres)12          |

|   | 1.7  | Efficiency12                      |

|   | 1.8  | Isolation12                       |

|   | 1.9  | Fault Protection                  |

| 2 | Мо   | odule Layout Guidelines13         |

|   | 2.1  | VRM Connector                     |

|   | 2.2  | Mechanical Dimensions15           |

| 3 | En   | vironmental Conditions17          |

|   | 3.1  | Operating Temperature17           |

|   | 3.2  | VRM Board Temperature17           |

|   | 3.3  | Non-Operating Temperature17       |

|   | 3.4  | Humidity17                        |

|   | 3.5  | Altitude17                        |

|   | 3.6  | Electrostatic Discharge17         |

|   | 3.7  | Shock and Vibration               |

|   | 3.8  | Electromagnetic Compatibility     |

|   | 3.9  | Reliability                       |

|   | 3.10 | Safety                            |

#### **Applications and Terminology**

This document defines one or more DC-to-DC converters to meet the power requirements of computer systems using Intel microprocessors. It does not attempt to define a specific voltage regulator module (VRM) implementation. VRM requirements will vary according to the needs of different computer systems, including the range of processors a specific VRM is expected to support in a system. The "VRM" designation refers to a voltage regulator module that is plugged into a system board.

The VRM 9.1 definition is specifically intended to meet the needs of processors using the 603-pin socket, in multi-processor platforms.

Each guideline is placed into one of three categories. The category immediately follows the section heading and is one of the following:

| REQUIRED | An essential part of the design—necessary to meet processor voltage and current specifications and follow processor layout guidelines.                                         |

|----------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| EXPECTED | Part of Intel's processor power definitions; necessary for consistency<br>among the designs of many systems and power devices. May be specified<br>or expanded by system OEMs. |

| PROPOSED | Normally met by this type of DC-to-DC converter and, therefore, included as a design target. May be specified or expanded by system OEMs.                                      |

## **1** Electrical Specifications

#### **1.1 Output Requirements**

#### 1.1.1 Voltage and Current

The VRM 9.1 Voltage Regulator Module is a DC-DC converter that supplies the correct voltage and current to a single processor, or when paralleled with other like converters, supplies the required voltage and current to multiple processors whose Vcc and Vss are also connected in parallel.

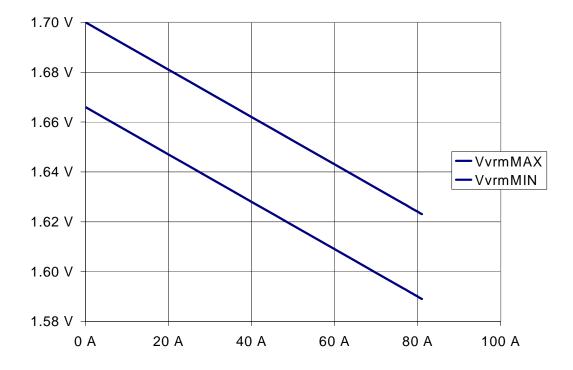

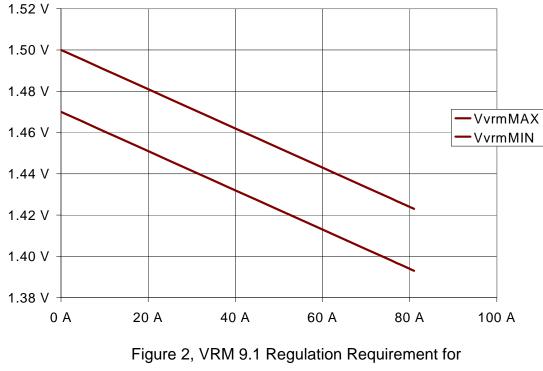

One VRM per processor is assumed. Current requirements are shown in Table 1. The maximum output voltage is determined by the five-bit VID code provided to the VRM, as described in Section 1.3.2. The system baseboard must supply additional decoupling capacitance and sufficient power and ground plane area to properly carry the DC currents. The required V-I relationship for the Intel<sup>®</sup> Xeon<sup>TM</sup> processor is given in Figure 1, and the one for the Intel Xeon Processor with 512 KByte L2 cache is in Figure 2.

Processor data are shown for reference. The corresponding processor data sheet takes precedence for processor specifications.

#### 1.1.2 Maximum Ratings

To supply the anticipated requirements of planned processor versions, VRM 9.1 should be able to provide a sustained output current of 81A. Refer to Table 1 for maximum design parameters.

| Symbol               | Parameter                                         | Unit | Value            |

|----------------------|---------------------------------------------------|------|------------------|

| Icc <sub>MIN</sub>   | Minimum current drawn by a single processor       | А    | 0.5 <sup>1</sup> |

| ICCACTIVE            | Maximum step current change by a single processor | А    | 54               |

| Icc <sub>MAX</sub>   | Maximum total current drawn by a single processor | А    | 75               |

| Ivrm <sub>MAX</sub>  | Maximum current required <sup>2</sup>             | А    | 81               |

| lvrm <sub>SLEW</sub> | VRM output current slew rate <sup>3</sup>         | A/μs | 50               |

| Table 1, VRM 9.1 Current Requirements | Table 1, | VRM 9.1 | Current | Requir | ements |

|---------------------------------------|----------|---------|---------|--------|--------|

|---------------------------------------|----------|---------|---------|--------|--------|

1. Estimate of lowest current state for VRM regulation, not to be construed as a processor specification. Refer to data sheet for actual design information.

2. Includes tolerance for needs of current sharing

3. Typical value for slew rate. Actual requirement will depend on decoupling of actual VRM and baseboard. Slew rate of processor load at the socket is 450A/µs.

#### 1.1.3 Output Voltage Tolerance

#### REQUIRED

The remote sense lines of each VRM should be routed on the system board to a remote sense point at the geometric center of the processors, where they are connected to each other and to the Vcc and Vss planes. The VRM regulates this point as follows:

- Vvrm<sub>MIN</sub> = 0.980 \* VID\_Setpoint\_Voltage VRM\_Output\_Current \* 0.95mΩ

- Vvrm<sub>MAX</sub> = VID\_Setpoint\_Voltage VRM\_Output\_Current \* 0.95mΩ

- Vvrm<sub>MIN</sub> and Vvrm<sub>MAX</sub> are VRM voltage regulation requirements measured at the power plane reference point (VRM remote-sense star connection at the geometric center of the processor loads on the system board).

- Vvrm<sub>MIN</sub> is the minimum voltage allowed for a given VRM output current.

- Vvrm<sub>MAX</sub> is the maximum voltage allowed for a given VRM output current.

See example load lines in Figure 1 and Figure 2 and their corresponding numerical values in Table 2. The VRM shall regulate as defined above for all VID set-points (except during input voltage turn-on and turn-off. See Section 1.1.6 for turn-on and turn-off tolerances).

Voltage tolerance includes:

- Initial DC output voltage set-point error

- Component aging effects

- Output ripple and noise from DC to 100MHz

- Full ambient temperature range and warm up

- Static operation

- Dynamic output load changes

- Input voltage variations

Figure 1, VRM 9.1 Regulation Requirement for Intel<sup>®</sup> Xeon<sup>™</sup> Processor (VID = 1.7V)

Intel<sup>®</sup> Xeon<sup>™</sup> Processor with 512 KByte L2 Cache (VID = 1.5V)

| B                                    |                                |                                                                                                      |                     |                            | •                                    |                     |                     |                                                              |                     |

|--------------------------------------|--------------------------------|------------------------------------------------------------------------------------------------------|---------------------|----------------------------|--------------------------------------|---------------------|---------------------|--------------------------------------------------------------|---------------------|

| VRM<br>Output<br>Current,<br>Amperes | with 512<br>Cache (V<br>Remote | on Processor<br>2 KByte L2<br>(VID = 1.5V) Intel Xeon Processor<br>ote Sense<br>oltage Sense Voltage |                     |                            | VRM<br>Output<br>Current,<br>Amperes |                     |                     | Intel Xeon Processor<br>(VID = 1.7V) Remote<br>Sense Voltage |                     |

|                                      | Vvrm <sub>MAX</sub>            | Vvrm <sub>Min</sub>                                                                                  | Vvrm <sub>MAX</sub> | V <b>∨rm<sub>Min</sub></b> |                                      | Vvrm <sub>MAX</sub> | V∨rm <sub>Min</sub> | Vvrm <sub>MAX</sub>                                          | Vvrm <sub>Min</sub> |

| 0                                    | 1.500                          | 1.470                                                                                                | 1.700               | 1.666                      | 42                                   | 1.460               | 1.430               | 1.660                                                        | 1.626               |

| 2                                    | 1.498                          | 1.468                                                                                                | 1.698               | 1.664                      | 44                                   | 1.458               | 1.428               | 1.658                                                        | 1.624               |

| 4                                    | 1.496                          | 1.466                                                                                                | 1.696               | 1.662                      | 46                                   | 1.456               | 1.426               | 1.656                                                        | 1.622               |

| 6                                    | 1.494                          | 1.464                                                                                                | 1.694               | 1.660                      | 48                                   | 1.454               | 1.424               | 1.654                                                        | 1.620               |

| 8                                    | 1.492                          | 1.462                                                                                                | 1.692               | 1.658                      | 50                                   | 1.453               | 1.423               | 1.653                                                        | 1.619               |

| 10                                   | 1.491                          | 1.461                                                                                                | 1.691               | 1.657                      | 52                                   | 1.451               | 1.421               | 1.651                                                        | 1.617               |

| 12                                   | 1.489                          | 1.459                                                                                                | 1.689               | 1.655                      | 54                                   | 1.449               | 1.419               | 1.649                                                        | 1.615               |

| 14                                   | 1.487                          | 1.457                                                                                                | 1.687               | 1.653                      | 56                                   | 1.447               | 1.417               | 1.647                                                        | 1.613               |

| 16                                   | 1.485                          | 1.455                                                                                                | 1.685               | 1.651                      | 58                                   | 1.445               | 1.415               | 1.645                                                        | 1.611               |

| 18                                   | 1.483                          | 1.453                                                                                                | 1.683               | 1.649                      | 60                                   | 1.443               | 1.413               | 1.643                                                        | 1.609               |

| 20                                   | 1.481                          | 1.451                                                                                                | 1.681               | 1.647                      | 62                                   | 1.441               | 1.411               | 1.641                                                        | 1.607               |

| 22                                   | 1.479                          | 1.449                                                                                                | 1.679               | 1.645                      | 64                                   | 1.439               | 1.409               | 1.639                                                        | 1.605               |

| 24                                   | 1.477                          | 1.447                                                                                                | 1.677               | 1.643                      | 66                                   | 1.437               | 1.407               | 1.637                                                        | 1.603               |

| 26                                   | 1.475                          | 1.445                                                                                                | 1.675               | 1.641                      | 68                                   | 1.435               | 1.405               | 1.635                                                        | 1.601               |

| 28                                   | 1.473                          | 1.443                                                                                                | 1.673               | 1.639                      | 70                                   | 1.434               | 1.404               | 1.634                                                        | 1.600               |

| 30                                   | 1.472                          | 1.442                                                                                                | 1.672               | 1.638                      | 72                                   | 1.432               | 1.402               | 1.632                                                        | 1.598               |

| 32                                   | 1.470                          | 1.440                                                                                                | 1.670               | 1.636                      | 74                                   | 1.430               | 1.400               | 1.630                                                        | 1.596               |

| 34                                   | 1.468                          | 1.438                                                                                                | 1.668               | 1.634                      | 76                                   | 1.428               | 1.398               | 1.628                                                        | 1.594               |

| 36                                   | 1.466                          | 1.436                                                                                                | 1.666               | 1.632                      | 78                                   | 1.426               | 1.396               | 1.626                                                        | 1.592               |

| 38                                   | 1.464                          | 1.434                                                                                                | 1.664               | 1.630                      | 80                                   | 1.424               | 1.394               | 1.624                                                        | 1.590               |

| 40                                   | 1.462                          | 1.432                                                                                                | 1.662               | 1.628                      | 82                                   | 1.422               | 1.392               | 1.622                                                        | 1.588               |

Table 2, Intel<sup>®</sup> Xeon<sup>™</sup> Processor VRM Regulation Requirements

#### 1.1.4 No-Load Operation

The VRM shall operate at all load conditions from maximum current down to zero load. In practice the VID code generated when no processors are installed (true zero-load condition) will turn off the VRM output. During 'no load' conditions the VRM does not need to meet the output regulation specifications described in Section 1.1.3, but its output must not exceed 110% of the value of the maximum DC output voltage (VID set-point voltage), and it must not trigger overvoltage fault detection circuitry.

When the VRM is loaded with the  $Icc_{MIN}$  listed in Table 1, it must regulate and source current without triggering failures or causing control signal malfunction.

#### 1.1.5 Turn-on Response Time

The output voltage should reach its specified range within 15ms after the input power reaches its minimum voltage and the OUTEN signal is asserted.

#### 1.1.6 Overshoot and Undershoot at Turn-On or Turn-Off

Overshoot must be less than 2% above the Voltage Identification (VID) code. No negative voltage below -0.1V may be present at the output at any time.

#### REQUIRED

**EXPECTED**

REQUIRED

#### 8

#### 1.1.7 Converter Stability

The VRM, operating independently or paralleled with other VRMs, needs to be unconditionally stable under all output voltage ranges and current transients with system board capacitance ranging from 5.000  $\mu$ F to 20.000  $\mu$ F and with less than 2.0m $\Omega$  ESR.

#### 1.1.8 Current Sharing

Multi-processor applications require that current-sharing capability be available to avoid powerplane splits.

One pin of the VRM is reserved for control of star-point or single-wire current sharing. This pin will be connected to other VRMs within the system. VRMs designed for current sharing by means of accurate output control need not use this pin. If a VRM does not use the current share pin, the pin should not be connected on the module.

There is no time limit for response to power-up or transients: VRMs must meet all other electrical specifications during transitions, and output current levels must not damage the VRMs.

#### 1.1.8.1 Current Sharing Tolerance

The output current of any VRM should match the output current of all paralleled VRMs within 10% of the rated output current over the full output current range, except during initial power-up. For instance, if a particular VRM model is designed to supply a 50A processor as a maximum, the difference between the output currents of two or more VRMs in parallel may be as much as 5A at any value of current actually produced, even to the point where one VRM is producing 5A, and one in parallel with it is producing no current in supplying a 5A load.

The VRM must supply current equal to the total load multiplied by the ratio of (1 + tol) and (n + tol) where "tol" is the current sharing accuracy and "n" is the number of VRMs sharing the load. Current sharing accuracy better than 10% would allow the VRM to be designed for a lower output current. It may more cost effective to design to a looser current sharing accuracy and a higher output current. For example, assuming a 300A load supplied by four parallel VRMs, each would need to be designed for 77.8A and 80.5A for respective current share accuracies of 5% and 10%.

#### 1.1.8.2 Interoperability Between Manufacturers

Current sharing among different VRM models, including VRMs from different manufacturers, is an expected feature. However, cost optimization and difficulties involved with fully testing interoperability may preclude use of this feature.

#### 1.1.8.3 Negative Current Limit

Because the output of the VRM will be connected in parallel with other voltage sources (other VRMs) the VRM should incorporate negative current limiting or equivalent functionality to protect the VRM from current from external voltage sources.

#### 1.1.8.4 Current Sharing Methodology

The method used to accomplish current sharing will depend upon the VRM design. The simplest method is to share unloaded set-point voltage references and rely on the drooping of the load line to force current sharing. If the shared error amplifier voltage method is used the VRMs must be of identical design. If auto-master/slave or current-average methods are used, then the Ishare bus

PROPOSED

**EXPECTED**

## REQUIRED

REQUIRED

## **EXPECTED**

#### REQUIRED

#### VRM 9.1 DC-DC Converter Design Guidelines

output should operate between 0 to 2V, representing 0 to 81A. Current sharing during transients is accomplished by adhering to the load line as defined in Figures 1 & 2 and Table 2 to a tolerance of  $\pm 3$  mV.

Hot-swapping capability is not a requirement.

## 1.2 Input Voltage and Current

#### 1.2.1 Input Voltages

The main power source for the VRM is 12V + 5%, -8%. This voltage is supplied by a conventional computer power supply through a cable to the system board. The system board will supply local bulk bypassing on the 12V rail. For input voltages outside the normal operating range, the VRM should either operate properly or shut down.

#### 1.2.2 Load Transient Effects on Input Current

When the VRM is providing an output current step to the load from Iout<sub>MIN</sub> to Iout<sub>MAX</sub> or Iout<sub>MAX</sub> to Iout<sub>MIN</sub> at the slew rate listed in Section 1.1.1, the slew rate of the input current to the VRM should not exceed 1.0A/us.

The system board needs sufficient bulk decoupling to ensure that the supply voltage on the system board does not go outside of regulation requirements during times of transient load on the VRM(s).

## **1.3 Control Inputs**

Control inputs should accept an open-collector, open-drain, open-switch-to-ground, low-voltage TTL or low-voltage CMOS signal.

#### 1.3.1 Output Enable—(OUTEN)

The VRM must accept an input signal to enable the output. An open-circuit or active high enables the VRM and a ground or active low disables the VRM. The input should have an internal pull-up resistor between  $1k\Omega$  and  $10k\Omega$  to 3.3 or 5.0 volts. The maximum low-input voltage is 0.8V; the minimum high-input voltage is 1.7V. These inputs should be capable of withstanding up to 5.5V.

When disabled, the VRM should sink less than 100mA from the 12V Input and less than 1A from shared VRMs that remain on

#### 1.3.2 Voltage Identification—(VID[4:0])

The VRM must accept five lines to set the nominal (maximum) voltage as defined by the table below. Five processor package pins will have a high-low pattern corresponding to the voltage required by the individual processor. When all five VID inputs are high (11111), the VRM should disable its output.

The maximum low-input voltage is 0.8V; the minimum high-input voltage is 1.7V. Each VID input should have a 1 k $\Omega \pm 10\%$  pull-up resistor to  $3.3V \pm 5\%$ .

EXPECTED

EXPECTED

## REQUIRED

REQUIRED

REQUIRED

| Proc | Vcc  | <b>Processor Pins</b> $(0 = low, 1 = high)$ |      |      |       | high) | Vcc  |      |      |      |      |             |

|------|------|---------------------------------------------|------|------|-------|-------|------|------|------|------|------|-------------|

| VID4 | VID3 | VID2                                        | VID1 | VID0 | (V)   |       | VID4 | VID3 | VID2 | VID1 | VID0 | <b>(V</b> ) |

| 1    | 1    | 1                                           | 1    | 1    | Off   | -     | 0    | 1    | 1    | 1    | 1    | 1.475       |

| 1    | 1    | 1                                           | 1    | 0    | 1.1   |       | 0    | 1    | 1    | 1    | 0    | 1.5         |

| 1    | 1    | 1                                           | 0    | 1    | 1.125 | _     | 0    | 1    | 1    | 0    | 1    | 1.525       |

| 1    | 1    | 1                                           | 0    | 0    | 1.15  |       | 0    | 1    | 1    | 0    | 0    | 1.55        |

| 1    | 1    | 0                                           | 1    | 1    | 1.175 |       | 0    | 1    | 0    | 1    | 1    | 1.575       |

| 1    | 1    | 0                                           | 1    | 0    | 1.2   | -     | 0    | 1    | 0    | 1    | 0    | 1.6         |

| 1    | 1    | 0                                           | 0    | 1    | 1.225 |       | 0    | 1    | 0    | 0    | 1    | 1.625       |

| 1    | 1    | 0                                           | 0    | 0    | 1.250 |       | 0    | 1    | 0    | 0    | 0    | 1.65        |

| 1    | 0    | 1                                           | 1    | 1    | 1.275 |       | 0    | 0    | 1    | 1    | 1    | 1.675       |

| 1    | 0    | 1                                           | 1    | 0    | 1.3   |       | 0    | 0    | 1    | 1    | 0    | 1.7         |

| 1    | 0    | 1                                           | 0    | 1    | 1.325 |       | 0    | 0    | 1    | 0    | 1    | 1.725       |

| 1    | 0    | 1                                           | 0    | 0    | 1.35  |       | 0    | 0    | 1    | 0    | 0    | 1.75        |

| 1    | 0    | 0                                           | 1    | 1    | 1.375 |       | 0    | 0    | 0    | 1    | 1    | 1.775       |

| 1    | 0    | 0                                           | 1    | 0    | 1.4   |       | 0    | 0    | 0    | 1    | 0    | 1.8         |

| 1    | 0    | 0                                           | 0    | 1    | 1.425 |       | 0    | 0    | 0    | 0    | 1    | 1.825       |

| 1    | 0    | 0                                           | 0    | 0    | 1.45  |       | 0    | 0    | 0    | 0    | 0    | 1.85        |

Table 3, Voltage Identification (VID)

## 1.4 Remote Sense (VO-sen+, VO-sen-)

## EXPECTED

A star remote sense connection should be provided at the geometric center of the processors to allow the VRM to sense voltage and compensate for an output voltage offset of 55mV in the power distribution path. VO-sen+ is the + sense line, and VO-sen– is the sense return. Differential sense inputs are required. In the event of an open sense line the VRM should maintain regulation through a local sense resistor on the VRM board. Systems that do not use remote sense will not connect these lines on the system board. The remote sense lines should draw no more than 10mA, to minimize offset errors.

## 1.5 Power Good Output (PWRGD)

The VRM must provide an open collector or equivalent Power Good signal consistent with TTL DC levels. This signal should transition to the open (>100k $\Omega$ ) state within 10ms of the output voltage stabilizing within the range specified in Section 1.1.1. The signal should be in the low-impedance (to ground) state whenever Vout<sub>VRM</sub> is outside of the required range below and be in the open state whenever Vout<sub>VRM</sub> is within the range specified in Section 1.1.3. On power up, the PWRGD signal must remain in the low-impedance state until the output voltage has stabilized within the required tolerance.

## 1.5.1 Power Good Threshold Voltages

The minimum voltage at which PWRGD is asserted should be the  $Vvrm_{MIN}$  specified in Section 1.1.3, minus margin to prevent false de-assertion, but at least 95% of (VID minus 125mV).

The maximum voltage at which PWRGD is asserted should be the VID (set-point) voltage, plus margin to prevent false de-assertion, but should be no greater than VID plus 250mV.

## REQUIRED

Minimum Vtrip should be: The VID set-point voltage

plus 55mV to compensate for remote sense plus margin to prevent false trips.

1.5.2 Power Good Operation

This PWRGD output should be capable of sinking up to 4mA, while maintaining a voltage of 0.4V or lower. When the output is in the open state it should be capable of withstanding up to 5.5V. Latch-up or damage cannot occur if the pull-up voltage on the system board is present with no +12V input present.

VRM Power Good should remain low if the VRM is disabled by the Output Enable pin. System designers need to provide appropriate logic on the system board to decode VRM Power Good, VRM Enable, and system Power Good to prevent a false not-good condition (Power Good = low) when the VRM is disabled.

The VRM should be able to detect an internal failure and de-assert PWRGD even if the output is within the defined PWRGD range. It is sufficient for this purpose to detect whether all phases are switching at their output inductors. The intention of this provision is to detect failures independently when VRMs are sharing current to a common power plane in a multiple-processor system.

## 1.6 VRM Present (VRM-pres)

This line is ground when the VRM is installed. The system board can use this signal to detect the presence of each VRM installed in the system.

## 1.7 Efficiency

The efficiency of the VRM should be greater than 80% at maximum output current. It should not dissipate more power under any load condition than it does at maximum output current and maximum input voltage.

## 1.8 Isolation

Isolation from input to output is optional. A transformer-based topology may have advantages over a non-isolated buck converter: Over-voltage due to a shorted FET is eliminated, and duty cycles can be optimized to simplify control or improve efficiency. A common ground between input and output is required with an isolated topology.

## **1.9 Fault Protection**

These features are built into the VRM to prevent damage to the VRM or the circuits it powers.

## **1.9.1** Over Voltage Protection

The VRM should provide over-voltage protection (OVP) by including a circuit, separate from the voltage sense path, capable of shutting off the output drive when the output voltage rises beyond Vtrip. If practical, the protection circuit should also enable a low-resistance path to ground, so that no single component failure results in the output voltage rising above Vtrip. A non-resettable or resettable fuse may be included in the input of the VRM for this function. The response time should be such that the output voltage will not exceed VID plus 250mV.

#### VRM 9.1 DC-DC Converter Design Guidelines

#### **EXPECTED**

PROPOSED

PROPOSED

**EXPECTED**

Maximum Vtrip should be VID plus 250mV.

No combination of input voltage or output load sequences should falsely trigger an OVP event.

## 1.9.2 Fuse Protection for Power Input

The power input (12V) should be protected with a fuse rated not greater than 30A, which sustains all operating and inrush conditions and which "trips" only on catastrophic failure of the converter.

## 1.9.3 Overload Protection

The VRM should be capable of withstanding a continuous, abnormally low resistance on the output without damage or over-stress to the unit. Output current under this condition will be limited to no more than 150% of the maximum rated output of the VRM. Latching off or hiccup mode is acceptable during over-current conditions. The VRM should be capable of starting into a constant current load of 50% of maximum rated load current with maximum load capacitance, as defined in Section 1.1.7, without tripping the OCP circuitry. Errors in current sharing (see Section 1.1.8) during startup should not cause OCP circuits to shut down the converter.

## 1.9.4 Reset After Shutdown

If the VRM goes into a shutdown state due to a fault condition on its output (not an internal failure) it should return to normal operation after the fault has been removed, or after the fault has been removed and power has been cycled off and on.

## 2 Module Layout Guidelines

## 2.1 VRM Connector

The VRM interface with the system board is a 100mil-pitch, 62-pin edge connector, with an overall 3.95" length. The connector uses a retention clip or side latches to hold the VRM in place. The connector has a maximum rated temperature of 90°C, based on 2-oz. minimum copper lands on the VRM PCB and 19 contact pairs carrying 4.26A each.

## EXPECTED

## EXPECTED

PROPOSED

| Attributes      |                                  | VRM 9.0             | VRM 9.1   | VRM 9.1   |  |

|-----------------|----------------------------------|---------------------|-----------|-----------|--|

|                 |                                  | 12V Input           | 12V Input | 48V Input |  |

| Key Located be  | tween slots                      | 11, 12              | 12, 13    | 4, 5      |  |

| Omit Pin for Ke | ying                             | 6                   | 6         | 6         |  |

| Max Current pe  | r Contact Pair                   | 3.6 amps            | 4.26 amps | 4.26 amps |  |

| Max Current Ou  | utput – VRM                      | 68 amps             | 81 amps   | 81 amps   |  |

| Mounting        | Connector Style                  | Part Numbers (Tyco) |           |           |  |

|                 | Connector                        | 1364125-1           | 1489162-1 | 1489162-2 |  |

| Solder Tail     | Clip                             | 1364124-1           | 1364124-1 | 1364124-1 |  |

|                 | Connector with Latch             | 145432-3            | N/A       | N/A       |  |

|                 | Connector with Latch Supports    | 1364666-1           | 1489165-1 | 1489165-2 |  |

| Press Fit       | Press Fit Connector, clip, latch |                     | †         |           |  |

Table 4, Connector Part Numbers and Descriptions

<sup>†</sup> Please contact vendor(s) for mounting and latching options.

See Table 5 for the VRM pin-out definitions.

| Pin             | Pin Function P        |                 | Function              | Pin | Function | Pin | Function |  |  |  |  |

|-----------------|-----------------------|-----------------|-----------------------|-----|----------|-----|----------|--|--|--|--|

| 1               | VIN+                  | 62              | VIN-                  | 16  | VO+      | 47  | VO+      |  |  |  |  |

| 2               | VIN+                  | 61              | VIN-                  | 17  | VO-      | 46  | VO-      |  |  |  |  |

| 3               | VIN+                  | 60              | VIN-                  | 18  | VO+      | 45  | VO+      |  |  |  |  |

| 4 <sup>1</sup>  | VIN+                  | 59 <sup>1</sup> | VIN-                  | 19  | VO-      | 44  | VO-      |  |  |  |  |

| 5 <sup>1</sup>  | Reserved <sup>3</sup> | 58 <sup>1</sup> | VRM-pres              | 20  | VO+      | 43  | VO+      |  |  |  |  |

| 6               | key                   | 57              | VID4                  | 21  | VO-      | 42  | VO-      |  |  |  |  |

| 7               | VID3                  | 56              | VID2                  | 22  | VO+      | 41  | VO+      |  |  |  |  |

| 8               | VID1                  | 55              | VID0                  | 23  | VO-      | 40  | VO-      |  |  |  |  |

| 9               | Reserved <sup>3</sup> | 54              | Ishare                | 24  | VO+      | 39  | VO+      |  |  |  |  |

| 10              | PWRGD                 | 53              | OUTEN                 | 25  | VO-      | 38  | VO-      |  |  |  |  |

| 11              | VO-sen-               | 52              | VO-sen+               | 26  | VO+      | 37  | VO+      |  |  |  |  |

| 12 <sup>2</sup> | Reserved <sup>3</sup> | 51 <sup>2</sup> | Reserved <sup>3</sup> | 27  | VO-      | 36  | VO-      |  |  |  |  |

| 13 <sup>2</sup> | VO-                   | 50 <sup>2</sup> | VO+                   | 28  | VO+      | 35  | VO+      |  |  |  |  |

| 14              | VO+                   | 49              | VO+                   | 29  | VO-      | 34  | VO-      |  |  |  |  |

| 15              | VO-                   | 48              | VO-                   | 30  | VO+      | 33  | VO+      |  |  |  |  |

|                 |                       |                 |                       | 31  | VO-      | 32  | VO-      |  |  |  |  |

Table 5, VRM Pins

<sup>1</sup>A single notch between pins 4&5 and between pins 58&59 is reserved for +48V input VRMs <sup>2</sup> A single notch between pins 12&13 and between pins 50&51 identifies a +12V-input VRM <sup>3</sup> Reserved pins can be used for an I<sup>2</sup>C interface:

I2C\_CLK 5

- 9 I2C\_DATA

- 12 I2C A0

- 51 I2C\_A1

## 2.2 Mechanical Dimensions

#### PROPOSED

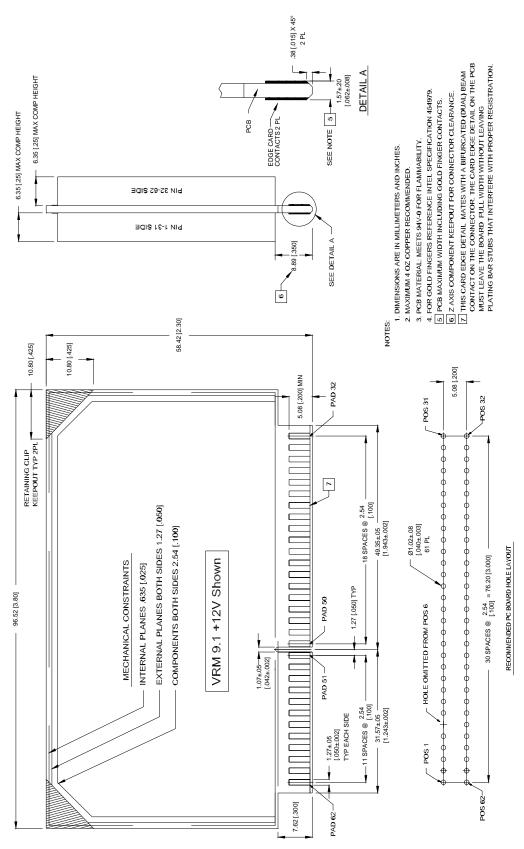

The maximum outline dimensions of the VRM should be as shown in Figure 3:

Figure 3, VRM Footprint and Space Requirements

## **3** Environmental Conditions

The VRM design, including materials, should be consistent with the manufacture of units that meet the environmental requirements specified below.

## 3.1 Operating Temperature

The VRM should meet all electrical requirements when operated over an ambient temperature of  $0^{\circ}$ C to  $+60^{\circ}$ C at full load with a minimum airflow of 400 LFM.

Operating conditions should be considered to include 10 cycles between min and max temperature at a rate of 10°C/hour and a dwell time of 30 minutes at extremes.

## 3.2 VRM Board Temperature

To maintain the connector within its operating temperature range, the board temperature at the connector interface, cannot exceed a temperature of 90°C.

At no time during operation is the board permitted to exceed  $90^{\circ}$ C within a distance of 2.54 mm [.100 in] from the top of the connector (0.4" from board edge). In order not to exceed  $90^{\circ}$ C, it is recommended that the board be constructed from 2 ounce copper cladding.

The VRM board must contain gold lands (fingers) for interfacing with the VRM connector that are  $1.27 \pm 0.05 \text{ mm} [.050 \pm .002 \text{ in}]$  wide by 5.08 mm [.200 in] minimum long and spaced  $2.54 \pm 0.05 \text{ mm} [.100 \pm .002 \text{ in}]$  apart. Traces from the lands to the power plane should be a minimum of 0.89 mm [.035 in] wide and of a minimal length.

## 3.3 Non-Operating Temperature

The VRM should not be damaged when exposed to temperatures between  $-40^{\circ}$ C and  $+70^{\circ}$ C. These should be considered to include 50 cycles of min to max temperatures at 20°/hour with a dwell time of 20 minutes at extremes

## 3.4 Humidity

85% relative - operating

95% relative - non-operating

## 3.5 Altitude

10k feet - operating

50k feet - non-operating

## 3.6 Electrostatic Discharge

Testing should be in accordance with IEC 61000-4-2.

Operating – 15kV initialization level. The direct ESD event should cause no out-of-regulation conditions – including overshoot, undershoot and nuisance trips of over-voltage protection, over-current protection or remote shutdown circuitry.

Non-operating - 25kV initialization level. The direct ESD event should not cause damage to VRM circuitry.

#### PROPOSED

PROPOSED

## PROPOSED

REQUIRED

PROPOSED

PROPOSED

## 3.7 Shock and Vibration

The VRM should not be damaged and the interconnect integrity not compromised during:

- A shock of 50G with an 11 millisecond half sine wave, non-operating, the shock to be applied in each of the orthogonal axes.

- Vibration of 0.01G<sup>2</sup> per Hz at 5 Hz, sloping to 0.02G<sup>2</sup> per Hz at 20 Hz and maintaining 0.02G<sup>2</sup> per Hz from 20 Hz to 500 Hz, non-operating, applied in each of the orthogonal axes.

## 3.8 Electromagnetic Compatibility

Design, including materials, should be consistent with the manufacture of units that comply with the limits of FCC Class B and CISPR22 Class B for radiated emissions.

## 3.9 Reliability

Design, including materials, should be consistent with the manufacture of units with an MTBF of 500,000 hours of continuous operation at 55°C maximum, outputs loaded and worst-case line, while meeting specified requirements. MTBF should be calculated in accordance with MIL-STD-217F or Bellcore.

## 3.10 Safety

The VRM should be UL Recognized to standard UL1950 3rd Ed., including requirements of IEC950 and EN 60950. Plastic parts and printed wiring board are to be UL Recognized with 94V-0 flame class.

#### PROPOSED

PROPOSED

PROPOSED

#### PROPOSED

#### 18