# **3rd Generation Intel XScale**<sup>®</sup> **Microarchitecture**

**Software Design Guide**

July 2007

Order Number: 315058-001US

INFORMATION IN THIS DOCUMENT IS PROVIDED IN CONNECTION WITH INTEL® PRODUCTS. NO LICENSE, EXPRESS OR IMPLIED, BY ESTOPPEL OR OTHERWISE, TO ANY INTELLECTUAL PROPERTY RIGHTS IS GRANTED BY THIS DOCUMENT. EXCEPT AS PROVIDED IN INTEL'S TERMS AND CONDITIONS OF SALE FOR SUCH PRODUCTS, INTEL ASSUMES NO LIABILITY WHATSOEVER, AND INTEL DISCLAIMS ANY EXPRESS OR IMPLIED WARRANTY, RELATING TO SALE AND/OR USE OF INTEL PRODUCTS INCLUDING LIABILITY OR WARRANTIES RELATING TO FITNESS FOR A PARTICULAR PURPOSE, MERCHANTABILITY, OR INFRINGEMENT OF ANY PATENT, COPYRIGHT OR OTHER INTELLECTUAL PROPERTY RIGHT. Intel products are not intended for use in medical, life saving, life sustaining, critical control or safety systems, or in nuclear facility applications.

Intel may make changes to specifications and product descriptions at any time, without notice.

Intel Corporation may have patents or pending patent applications, trademarks, copyrights, or other intellectual property rights that relate to the presented subject matter. The furnishing of documents and other materials and information does not provide any license, express or implied, by estoppel or otherwise, to any such patents, trademarks, copyrights, or other intellectual property rights.

Designers must not rely on the absence or characteristics of any features or instructions marked "reserved" or "undefined." Intel reserves these for future definition and shall have no responsibility whatsoever for conflicts or incompatibilities arising from future changes to them.

Intel processor numbers are not a measure of performance. Processor numbers differentiate features within each processor family, not across different processor families. See <a href="http://www.intel.com/products/processor\_number">http://www.intel.com/products/processor\_number</a> for details.

The 3rd Generation Microarchitecture may contain design defects or errors known as errata which may cause the product to deviate from published specifications. Current characterized errata are available on request.

Contact your local Intel sales office or your distributor to obtain the latest specifications and before placing your product order.

Copies of documents which have an order number and are referenced in this document, or other Intel literature may be obtained by calling 1-800-548-4725 or by visiting Intel's website at http://www.intel.com.

BunnyPeople, Celeron, Celeron Inside, Centrino, Centrino logo, Core Inside, Dialogic, FlashFile, i960, InstantIP, Intel, Intel logo, Intel386, Intel486, Intel740, IntelDX4, IntelSX2, Intel Core, Intel Inside, Intel Inside logo, Intel. Leap ahead., Intel. Leap ahead. logo, Intel NetBurst, Intel NetMerge, Intel NetStructure, Intel SingleDriver, Intel SpeedStep, Intel StrataFlash, Intel Viiv, Intel VPro, Intel XScale, IPLink, Itanium, Itanium Inside, MCS, MMX, Oplus, OverDrive, PDCharm, Pentium, Pentium Inside, skoool, Sound Mark, The Journey Inside, VTune, Xeon, and Xeon Inside are trademarks or registered trademarks of Intel Corporation or its subsidiaries in the United States and other countries.

July 2007

Order Number: 315058-001US

The ARM\* and ARM Powered logo marks (the ARM marks) are trademarks of ARM, Ltd., and Intel uses these marks under license from ARM, Ltd. \*Other names and brands may be claimed as the property of others.

Copyright © 2007, Intel Corporation. All Rights Reserved.

# **Contents**

| 1.0       | Intro<br>1.1<br>1.2 | oduction  Quick Porting Guide  Use of Coprocessors                                          | 5              |  |  |  |

|-----------|---------------------|---------------------------------------------------------------------------------------------|----------------|--|--|--|

| 2.0       |                     | System Initialization and Reset                                                             |                |  |  |  |

|           | 2.1<br>2.2          | ConfigurationSoft Reset                                                                     | 13             |  |  |  |

| 3.0       | Men                 | Memory                                                                                      |                |  |  |  |

|           | 3.1<br>3.2<br>3.3   | Virtual Memory (MMU) Cache Management Aborts                                                | 16<br>25<br>51 |  |  |  |

|           | 3.4                 | Memory Barriers                                                                             | 55             |  |  |  |

| 4.0       | Perf                | formance Monitoring (PMU)                                                                   | 59             |  |  |  |

| 5.0       | Inte                | errupts                                                                                     | 62             |  |  |  |

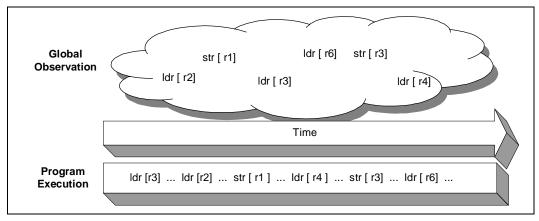

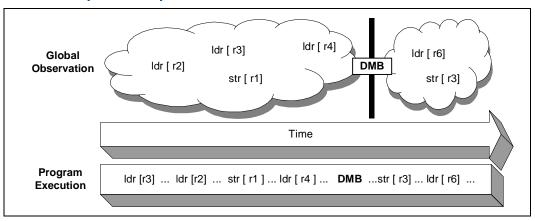

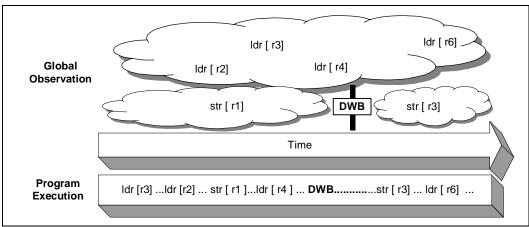

| Fig 1 2 3 | Da                  | bbal Observation vs. Program Executionta Memory Barrier Operationta Write Barrier Operation | 56             |  |  |  |

| Tab       | oles                |                                                                                             |                |  |  |  |

| 1         | SE                  | Bit Scenarios                                                                               | 6              |  |  |  |

# **Revision History**

| Da     | te  | Revision | Description      |

|--------|-----|----------|------------------|

| July 2 | 007 | 001      | Initial release. |

# 1.0 Introduction

This design guide contains routines for OS, monitor and device driver writers. It is generally not of interest for user-level code. Also, it is not intended to be an optimization how-to guide. What it does contain are routines and code sequences that are reference examples and templates necessary for system software to function correctly on 3rd generation Intel XScale® microarchitecture¹ (3rd generation microarchitecture or microarchitecture).

## 1.1 Quick Porting Guide

This section summarizes some significant changes in the 3rd generation microarchitecture. Subsequent sections give more details and code suggestions.

#### 1.1.1 L2 Cache

The 3rd generation microarchitecture introduces a physically tagged, physically indexed, L2 cache (Section 3.2.6). Availability of the L2 cache varies by product. This typically has minimal impact on the OS with the following exceptions.

- System initialization code, at the appropriate time, enables the L2.

- Pages containing page table descriptors are marked as L2 cacheable. In addition, the table walk outer cache attribute, in the translation table base register, must be set to 0b11 (Outer Write Back) to allow the 3rd generation microarchitecture to hit the cached page descriptors.

Page table descriptor L2 cacheability and the table walk outer cache attribute must be enabled together, or disabled together, to ensure consistency between software and the processor microarchitecture.

<sup>1.</sup> ARM\* architecture compliant.

#### 1.1.2 Shared Bit

The shared bit is a new page attribute enabling cache coherency for memory shared by multiple agents. The shared bit marks pages that are shared between the 3rd generation microarchitecture and external devices. Not all products support I/O coherency (refer to the appropriate ASSP specification for more details.) Allowing the processor to manage I/O coherency achieves higher performance than using uncacheable memory regions.

Shared memory does not imply any specific memory ordering. For regions of memory that require more explicit access and timing controls see Memory Barriers below.

Do not use the S bit in Operating Systems without consideration. Performance is lower in some circumstances when the S bit is used and specific products that do not enable hardware coherency prohibit its use. See Table 1 for notes on use of the S bit.

#### Table 1. S Bit Scenarios

| S bit in page table entry | Product supports<br>hardware<br>coherency | L2 cache present | Effect                                                                                           |

|---------------------------|-------------------------------------------|------------------|--------------------------------------------------------------------------------------------------|

| 0                         | х                                         | х                | Normal operation. Coherence enforced by software.                                                |

| 1                         | х                                         | False            | Performance suffers because the machine<br>degrades memory accesses to "L1<br>uncacheable".      |

| 1                         | False                                     | x                | Unpredictable — do not use S bit when hardware does not support coherency.                       |

| 1                         | True                                      | True             | Performance is slightly lower because of coherency overhead. Coherency is supported by hardware. |

## 1.1.3 Memory Barriers

The 3rd generation microarchitecture optimizes memory accesses; this optimization causes external viewers of the microarchitecture to see memory operations in a different order than sequential execution implies. This reordering aids performance and does not alter the correctness of single-processor application programs. However, system software occasionally needs to control memory access order. Three new instructions were added to handle these situations. These instructions are:

- data memory barrier (DMB)

- data write barrier (DWB)

- pipeline flush (PF)

Refer to Section 3.2.8 for an example use of these instructions.

There are other methods to control memory ordering in addition to the three explicit instructions. This includes specific page table attributes and certain instructions which have a side-effect of synchronizing memory operations.

#### 1.1.4 **Miscellaneous Changes**

The 3rd generation microarchitecture introduces new cache management functions useful for system-level software. The L1 data cache is now cleaned by set and way. Also, a cache line is now cleaned and invalidated in one instruction (by either MVA or set and way, refer to Section 3.2.4).

The 3rd generation microarchitecture requires new L1 cache cleaning routines using the new instructions mentioned above. Cache cleaning routines from previous microarchitectures produces unreliable results. See Example 27 for a routine to clean the L1 D cache.

The 3rd generation microarchitecture no longer has a mini data cache. Instead, system software uses Low Locality of Reference (LLR) memory attributes. LLR has the same page table entry encoding as formerly used for the mini data cache. However, LLR is not always a direct functional replacement for the mini data cache. Evaluate each situation to ensure the correct behavior is achieved.

A specific routine to lock data into the L1 data cache has been defined in this document (Example 22). When data is locked in the L1, be sure to use this routine; variations from it does not operate correctly.

July 2007 Software Design Guide Order Number: 315058-001US

July 2007

Order Number: 315058-001US

# 1.2 Use of Coprocessors

Throughout this guide, ARM coprocessor access instructions are used to perform many operations. Many of these instructions, especially for control of the caches, do not use the value in the specified ARM register operand — a simple write to the co-processor causes the operation to occur.

According to the ARM Architecture Reference Manual, the contents of the ARM registers needs to be zero when the value is not used by the function. However, in most of the code sequences the specified ARM register contains some non-zero value, this value is ignored and the contents of the ARM register are not modified. This behavior is valid and is used for the 3rd generation microarchitecture, and the code sequences are able to avoid zeroing and using a scratch ARM register by depending on this behavior.

#### **System Initialization and Reset** 2.0

Certain tasks must be performed in order to initialize the 3rd generation microarchitecture after a system reset, and to perform a soft-reboot during a reset sequence. This section describes some routines that are utilized as part of these tasks.

#### 2.1 **Configuration**

This section describes operations relating to access of configuration and co-processor registers in the 3rd generation microarchitecture. Co-processor registers are accessed to control certain functions of the microarchitecture (such as cache enabling and disabling) as well as to perform specialized operations using other implementation specific co-processors.

Throughout this Guide, individual bits are turned on and off with a read-modify-write sequence on the CP15 ARM control register. Although in most examples only one bit is changed at a time (for example, turning BTB on/off, MMU on/off), it is possible to simultaneously enable multiple features in the ARM control register, by setting multiple bits at once. It is useful to do this in order to have a shorter configuration code sequence when multiple features of the 3rd generation microarchitecture need to be turned on or off at once.

# 2.1.1 Co-processor Access

Product specific co-processors are accessed using the co-processor access instructions in the 3rd generation microarchitecture. An example of this is accumulator functionality of co-processor 0. Within a running system, multiple applications want to use a single co-processor with an exclusive access view to it. In this case, it is desirable to have the co-processor state and its registers appear to be consistent and exclusively used by each process. When a process switches out with another it simply saves all the registers out to memory, so another process restores its old state and continue running.

The 3rd generation microarchitecture provides a mechanism for co-processor context switching to occur only when needed, by providing a co-processor access register, which allows system software to receive an undefined exception whenever an application accesses a specific co-processor. This is accomplished by clearing a bit in the Co-processor Access Register (CPAR). Each bit in the CPAR corresponds to a co-processor. When the bit is cleared, then access to the corresponding co-processor causes an undefined exception, which system software handles and uses to determine what action to take to ensure each process sees the co-processor in the state it last left if

#### Example 1. Setting Access Control Bits in the Co-processor Access Register

Example 1 sets Co-processor Access Register (CPAR) bit 0 based on the value of Rd. When Rd is zero, bit CPAR[0] is cleared, disabling access to co-processor 0 for any software that runs afterward. When software attempts to either read or write a co-processor 0 register, the 3rd generation microarchitecture produces an undefined exception. Since this is a precise exception, the exact state of the microarchitecture and which instruction caused the exception is determined. With this information system software is determined whether to allow the software to access the co-processor (and perhaps save and restore some state information) or to return an error to the process which caused the exception. Note, that at power-on-reset, all bits in the CPAR register are zero, so access to all co-processors is initially disabled.

An example of how system software utilizes the CPAR, is to allow multiple applications to have an exclusive view of a shared co-processor. Initially, access to the co-processor is disabled at boot time. When a process attempts to access the co-processor, an undefined exception occurs. The exception is handled and the co-processor being accessed is determined. At this point the exception handler decides when it needs to save the state of the co-processor, and also when it needs to load a saved state into the co-processor. When the co-processor is ready to be used by the current process, the handler code sets the corresponding bit in CPAR and exits the exception handler. The process that was accessing the co-processor continues as though the co-processor was always available and its state was consistent with when it was last context-switched.

#### **Synchronization (CPWAIT)** 2.1.2

At times, it is necessary to be able to ensure a point, after which a write to the ARM control register has taken effect. For example, when enabling memory address translation (turning on the MMU), it is vital to know when the MMU is actually ensured to be in operation. When the configuration routine returned and other software resumed before the MMU was enabled, memory accesses initially is affected in an unpredictable way.

The CPWAIT macro is a sequence of instructions which utilizes a read-after-write dependency, followed by a pipeline flush, to ensure changes to the ARM control register have taken effect before the next instruction executes.

Since any configuration operation on the ARM control register occurs with a write to a register in CP15, this macro works by issuing a read to a register in CP15. This read does not occur until after the previous writes have completed.

Additionally, reading this register causes a stall until the effect of the original configuration operation takes effect. In order to ensure execution stops before continuing any further, the next instruction after the read creates a load-use-dependency on the register used. This causes a stall until the previous read completes, along with any prior write operations.

The final instruction causes the pipeline to be flushed, which ensures that the next instruction executed must be re-fetched either out of cache when it exists there, or from main memory.

## **Example 2. CPWAIT Macro**

```

@ Use the following macro when software needs to be

@ assured that a CP15 update has taken effect.

@ It is only used while in a privileged mode, because it

@ accesses CP15. Rs is a scratch register.

.macro CPWAIT, Rs

mrc p15, 0, \Rs, c2, c0, 0 @ arbitrary read of CP15

mov \Rs, \Rs

@ wait for it

sub pc, pc, #4

@ flush the pipeline

@ At this point, any previous CP15 writes are

@ ensured to have taken effect.

endm

```

It is important to understand when it is necessary to utilize the CPWAIT macro. Because the macro ensures that all previous writes to CP15 have completed, it is not necessary to issue a CPWAIT after each write in a sequence of CP15 register writes, unless it was desired to have some part of the sequence take effect before the entire sequence completed.

Additionally it is not necessary to issue a CPWAIT immediately after a CP15 write, it is delayed and issued at a later time, and still ensures that the operation takes effect by the time the macro had completed.

Also, since CPWAIT does not explicitly change anything with respect to the configuration of the 3rd generation microarchitecture, it is important to remember that the effect of the original writes to CP15 are observed during or even before the issue of the CPWAIT macro. That is to say, although software cannot know exactly when the effect of a configuration operation is observed, it is ensured to be no later than the end of the CPWAIT sequence.

It is also useful to note that the entire code sequence above is not necessarily required for the CPWAIT operation to occur.

The Example 2 on page 11 works as a self-contained macro that is invoked from anywhere in the code. The macro creates its own dependency stall to ensure the 3rd generation microarchitecture stops executing until it has completed, but it does so by executing a dummy instruction after the read, to create the stall. When there was an instruction that generates a dependency on 'r0' that executes, after the read of the co-processor register, which is then used in its place.

For example, when desiring to invalidate the TLB immediately after disabling the MMU, a write to co-processor 15, using 'r0' (the contents are ignored) to invalidate the TLB just after the read, still ensures the disabling of the MMU takes effect, but result in a more compact code. An example of this 'short CPWAIT' is shown in "Soft Reset Sequence (Code Mapped 1:1)" on page 14.

Note:

This method does not also flush the pipeline. It is only suitable in a situation where the operation does not affect the code currently being executed (and any instructions already in the pipeline).

July 2007

Order Number: 315058-001US

#### 2.2 **Soft Reset**

Performing a soft reset in the 3rd generation microarchitecture, essentially involves returning the system to a power-on like-state and then branching to the reset vector to allow the system to boot again. It is important that certain components be returned to the power-on state in a specific order, or a situation occurs where the reset sequence causes a lockup, and the system is unable to reset or continue operation.

For example, when the L1 caches are disabled, but still contain valid lines, these produce cache hits when those memory locations are accessed, thaty cause errors when the system is restarting.

A similar problem occurs when the data or instruction TLB, the L2 cache, or the BTB have stale data, when a soft reset occurs.

The soft-reset sequence handles the case where the soft-reset code executes in a memory region, with the virtual and physical addresses mapped 1:1. That is to say, that the address the code resides at from the view of the software, is the same with the MMU enabled and disabled. In this case, the code is marked 'outer' cacheable in the page table entries describing the code, and there is no requirement to change this during the soft boot sequence.

In either case, it is essential that interrupts are disabled before this code is executed. This is because any execution of an interrupt handler causes the 3rd generation microarchitecture to branch from this code at an unknown point, possibly causing lines to be fetched in to the cache, or causing an abort loop when the handler code is no longer accessible (after the MMU is off).

Example 3 on page 14 illustrates the sequence of operations required to facilitate a soft-reset.

## Example 3. Soft Reset Sequence (Code Mapped 1:1)

```

@ This code must have a 1:1 virtual to physical memory mapping

@ This code is or is not marked 'outer cacheable' in its page table entry

@ This first instruction has the effect of disabling interrupts.

msr cpsr, #0xD3

@ Reset cpsr, F,I bits, SVC mode

GET_L2 PRESENT r0

@ macro call sets Z flag when L2 is not present

mov r0, #0

@ First unlock all caches and the TLBs

mcr p15, 0, r0, c9, c5, 1 @ unlock all lines in the L1 I-cache

@ unlock all lines in the L1 D-cache

mcr p15, 0, r0, c9, c6, 1

mcrne p15, 1, r0, c9, c5, 1 @ unlock all L2 cache lines, when L2 present mcr p15, 0, r0, c10, c4, 1 @ unlock the I-tlb mcr p15, 0, r0, c10, c8, 1 @ unlock the D-tlb

@ Disable the L1 data cache

mrc p15, 0, r0, c1, c0, 0 @ Get Control Register bic r0, r0, #0x0004 @ Clear C Bit (bit 2) mcr p15, 0, r0, c1, c0, 0 @ Update control register

@ When desired, branch to the L1 D-cache clean function here

bl l1_dcache_clean

bic r0, r0, #0x1800

@ Clear I Bit (bit 12), Z Bit (bit 11)

bic r0, r0, #0x0001

@ Clear M Bit (bit 0)

mcr p15, 0, r0, c1, c0, 0 @ Disable MMU, L1 I cache, and BTB mrc p15, 0, r0, c1, c0, 0 @ short CPWAIT mcr p15, 0, r0, c8, c7, 0 @ Invalidate I, D-TLB (stall on CPWAIT read) beg CLEANDONE

beq CLEANDONE

@ Jump over L2 clean when L2 not present

@ This code cleans and invalidates all lines in the L2 cache

mcr p15, 0, r0, c7, c10, 5 \,\,\, @ DMB Operation to impose memory fence.

GET L2 SIZE r0

@ low four bits returned in r0 are the L2

@ cache size, starting with 64 KB (0b0000)

@ increasing by powers of 2 (Example 30)

mov r1, #0xffffffe0

mov r2, #19

sub r2, r2, r0

@ determine the number of sets

@ clear out the extra bits when configuring

mov r0, r1, lsl r2

mov r0, r0, lsr r2

@ the number of sets

CLEANLOOP:

mcr p15, 1, r0, c7, c15, 2 @ clean and invalidate set/way in r0

adds r0, r0, #0x20000000 @ Increment shifted way index

bcc CLEANLOOP

@ Clean the next way when not done with this set

subs r0, r0, \#0x00000020 @ Decrement shifted set index

bpl CLEANLOOP

@ Go to next set when not at last one

mcr p15, 0, r0, c7, c10, 5 @ DMB Operation to impose memory fence.

CLEANDONE:

@ Reset microarchitecture registers to power-on-reset state.

mov r0, #0x0

mcr p15, 0, r0, c1, c0, 1

@ Reset Aux Control Register

mcr p15, 0, r0, c13, c0, 0 @ Process ID Register

mcr p15, 0, r0, c15, c1, 0 @ Co-processor Access Register

mcr p14, 0, r0, c0, c1, 0 @ PMU Control register

mcr p14, 0, r0, c4, c1, 0 @ PMU Interrupt enable register

mov r0, #0x1f

mcr p14, 0, r0, c5, c1, 0

@ PMU Overflow Flag Register

@ When applicable reset CP14 c7 and c6 to reset values.

@ Now restore the ARM control register to its power-on-reset state.

@ Note the L2 cannot be disabled once it has been enabled.

mrc p15, 0, r0, c1, c0, 0 @ Read Control Register

and r0, r0, #0x04000000 @ Clear all bits but L2 Enable

mcr p15, 0, r0, c1, c0, 0 @ write back value, reset to power on state

mcr p15, 0, r0, c1, c0, 0

@ Branch to zero (or reset handler)

mov pc, #0

```

As shown in Example 3 on page 14, in order to shut down the system, the components of the 3rd generation microarchitecture must be disabled in a particular order, to ensure that the reset code still executes during this time. Additionally, it is important that the system appear to be in a power-on-reset state when the final branch to the reset vector occurs

In order to ensure the processor is in a power-on reset state, the CPSR register is reset, to have interrupts disabled (F and I bits) and to be in supervisor mode. Then the next step is to unlock all entries in the L1 cache, L2 cache, and the TLB. This ensures the subsequent clean/invalidate operations work as expected, and not leave any locked valid entries behind.

After that the L1 data cache is disabled, then its contents are cleaned when desired, so any dirty cached data is cleaned and written out. The L1 instruction cache and BTB are also disabled. Cleaning the cache is or is not desired, depending on the specific application of the system software. In a case where dirty written data exists that needs to be cleaned out to some non-volatile storage, it needs to be cleaned before the system soft boots. In other cases, the system has already cleaned out all important data and any valid dirty lines in cache need not be written out.

It is important that the cache is disabled first and then emptied. This ensures that no new entries are created in the cache during or after the time it is cleaned and invalidated. This procedure is followed to ensure the L1 instruction cache and L2 cache are also emptied.

Now that the L1 Data and Instruction caches are disabled, the MMU is disabled. This effectively disables the L2 cache. After the MMU is off and no new TLB entries are fetched, the TLB is invalidated. Then, the L2 cache must be unlocked, cleaned when desired, and invalidated so that it is completely empty, since it is in a power on state.

Finally the L1 instruction cache, L1 data cache, and BTB are both invalidated so these are empty as well. The power-on-reset values of many co-processor registers are written out before the soft reboot occurs. This ensures that the processor behaves as though it had just powered on when the boot up code executes.

Note: The L2 cache cannot be disabled once it has been enabled, so it must be left enabled even during a soft reboot.

> Depending on the product configuration, Co-processor 14 registers 6 and 7 need to be reset to restore the power and clock modes. At this point, branching to the reset vector produce a reboot with the 3rd generation microarchitecture in the same state as though it had just been power cycled.

It is not possible to perform a soft reset of the 3rd generation microarchitecture with code that is not mapped 1:1. When using code that is not mapped 1:1 then the 1:1 code sequence must be copied to a page that is mapped 1:1 where the code is then executed. Treat this code as though it were self-modifying code as described in Chapter 3.2.8

3rd Generation Intel XScale® Microarchitecture Software Design Guide Order Number: 315058-001US

# 3.0 Memory

This section describes code sequences and examples which explain how system software utilizes memory related functions of the 3rd generation microarchitecture. Memory access in the microarchitecture is affected by:

- memory translation

- L1 caching

- L2 caching

- · memory barriers

# 3.1 Virtual Memory (MMU)

The MMU is a collection of hardware functions that implement virtual-to-physical memory address translation. The MMU contains:

- control registers

- the TLB

- translation table walk hardware

Access to the data and L2 caches is also controlled by enabling the MMU, because the page tables provide the cacheability information about the specific memory regions. Enabling the MMU is performed by code that is mapped 1:1 (virtual addresses match the translated physical addresses). Example 6 on page 19 shows a code fragment that enables the MMU.

#### Example 4. Creating a First Level Page Table

```

@ This code calls a function that sets up a first-level page table

@ of section descriptors. After it returns, it calls a function to create

@ a coarse 2nd level page table, and modifies the attributes of

@ the pages containing both page tables to have the correct cache attributes

@ for the microarchitecture.

@ The address where the table(s) need to reside is in r3.

@ Address where table needs to reside

mov r0, r3

bl create_1stlevel_table @ create table of sections, @ addr r0 1:1 mapped

add r4, r3, #16384 @ set r4 to the address just after the 1st

@ level table

mov r0, r4

mov r1, r3, lsr #20

mov r1, r1, lsl #20

@ put 1Meg aligned address of 1st table in r1

mov rı, rı, ısı #20 @ put 1Meg aligned address of 1st table in r1 bl create_coarse_table @ create table of 2nd level coarse descriptors

@ table @ addr r0, mapping for 1meg @ addr r1

@ Now set the correct 1st level descriptor to point to the 2nd level table.

mov r2, r3, lsr #20 @ put index of 1st level descriptor that

@ contains table into r2

ldr r2, [r3, r2]

@ load section descriptor

mov r2, r2, lsl #22

mov r2, r2, lsr #22 @ convert section descriptor to coarse pg tbl

orr r2, r2, r4

@ set coarse page table base address

bic r2, r2, #0xF

@ Clear section type, c,b bits

orr r2, r2, #0x1

@ Set coarse pg table type

@ Write coarse page table pointer back

str r2, [r3, r2]

mov r2, r3, lsl #12

@ Get index into 2nd level table

mov r2, r2, lsr #24

add r2, r2, r4

@ Get addr of coarse descriptors to modify

mov r0, #5

@ number of extended small pages to modify

ATTR LOOP:

ldr r1, [r2]

@ Load descriptor

bic r1, r1, #0xFF

@ Set Extended small page type, CB=00

orr r1, r1, #0x3

orr r1, r1, #0x170

@ Set Tex=101, AP=11

subs r0, r0, #1

str r1, [r2], #4

@ write back descriptor

bne ATTR LOOP

@ address to clean, invalidate from DCache

mov r1, r3

mov r0, #544

@ Clean 544 lines = 16k + 1k of tables

bl clean_inv_unlock

@ Call function

mcr p15, 0, r0, c7, c10, 4 @ Data Write Barrier

@ At this point, the first and second level tables written out have

@ the correct attributes in place for being updated while used, and

@ these are ready to be used by the MMU.

```

The code in Example 4 calls a function that creates a page table of section descriptors, which configure all virtual memory to have a 1-to-1 mapping with physical memory. Depending on particular system configuration, regions of address space are or are not marked cacheable in the L1 and L2 caches.

July 2007 Software Design Guide Order Number: 315058-001US

After creating the first level table, another function is called to create a second level table, located just after the first level table. The second level table contains pages which define attributes for 4 K of address space each. The second level descriptors, which map to the address range the table exists in, are modified as extended small page descriptors with L2 cacheability and no L1 cacheability. This ensures any page table writes, once it is being used by the MMU, do not need a cache clean/invalidate sequence, since these go directly to the L2. Any pages containing page tables must be marked L2 cacheable on the processor.

After the code has executed and the page table has been written, the L1 data cache lines that contain the modified data are cleaned and invalidated, and a data write barrier operation is executed. After this operation, it is possible to set the page table base register to the address of this table.

#### **Example 5. Creating a Supersection**

```

@ Create a supersection in the first level page table.

@ It assumes the first level page table is already created.

@ r1 = address of first level page table

@ r2 = 32-bit virtual address of start of supersection

@ r3 = bits 35:24 of supersection physical address in bits 11:0

mov r4, r2, lsr #20

@ Get the index into page table

add r4, r1, r4, lsl #2

@ multiply index by 4 (word offset into table)

@ and add to page table base address

mov r5, r3, lsl #24

@ put bits 7:0 of r3 into bits 31:24 of r5

mov r6, r3

bic r6, r6, #0xFF

add r5, r5, r6, lsl #12 @ put bits 11:8 of r3 into bits 23:20 of r5

@ At this point, r5 contains the supersection descriptor, which is repeated

@ for 16 entries (so it occupies 16 megs)

mov r0, #16

@ put count into r0

subs r0, r0, #1

@ decrement count

@ store descriptor and increment

str r5, [r4], #4

bne 1b

@ loop through all 16 entries

@ At this point VA r2 maps to 16-megabyte address space specified in bits

@ It is necessary to invalidate the instruction and data TLBs

@ at this point.

```

The code sequence in Example 5 creates a supersection, which maps the specified virtual address to the specified 36-bit physical address. It is assumed that the first level page table has already been created, and so only the supersection descriptors need to be written to.

The format of a supersection is similar to a section descriptor except that the upper 4 bits of the 36-bit physical address are stored in bits 23:20 of the descriptor, and bit 18 of the descriptor is set to designate that this is a supersection descriptor. The same supersection descriptor must be repeated for 16 consecutive page table entries, otherwise unpredictable behavior occurs.

After any change to the page table, it is necessary to invalidate the instruction and data TLBs, to clear out any stale entries. Also note, that page table updates must be managed carefully, when table walks are configured as L2 cacheable in the Translation Table Base register. Old page table entries were cached in the L2 cache and stores to the page table (when the MMU is disabled or the MMU enabled and the page table mapped to a L2 non-cacheable memory region) bypass the L2 cache.

July 2007

Order Number: 315058-001US

To avoid issues when table walks are L2 cacheable, it is recommended that the memory region containing the page table be marked as L2 cacheable in the page table and the MMU be enabled to allow the stores to be L2 cacheable.

Once the supersection is created, any access by the 3rd generation microarchitecture to the specified virtual address, causes the memory operation to access the specified 36-bit physical address. Access to 36-bit addresses only occurs when the MMU is enabled, because the actual address specified in code is still only 32-bits.

Example 6 shows a method of enabling the MMU on the 3rd generation microarchitecture. In order for the MMU to operate, a valid page table must exist in memory and its base address must be set in the Translation Table Base register (TTBASE).

Additionally the domains which are represented in the page table must be set up with the appropriate access in the domain access control register (DACR). Code executing memory operations from this point forward has the addresses translated by the page table entries, and has accesses checked against the access permission bits in the page section or page descriptor and the corresponding domain access bits in the DACR.

It is important that a CPWAIT instruction be used after the enabling of the MMU and before any code attempts to perform a memory operation. Using a CPWAIT allows the system software to ensure that the effect of the MMU being enabled is seen by any code that executes after the CPWAIT.

#### Example 6. Enable the MMU

```

@ Enable the MMU. Before enabling, make sure the page table base (TTBASE) is set,

@ and that the domain access control register (DACR) is configured as desired.

mrc p15, 0, r0, c1, c0, 0 @ Read the ARM control register

orr r0, r0, #0x1

mcr p15, 0, r0, c1, c0, 0 @ Enable the MMU

CPWAIT r0

```

Example 7 disables the operation of the MMU by turning off the MMU enable bit in the ARM control register. Since the L1 data cache cannot operate without the MMU, it is important that it be cleaned and disabled before the MMU is disabled.

Also note, that when the MMU is off, the L2 cache is effectively disabled, since any memory accesses are no longer able to see the attribute bits that enable L2 cacheability.

After the L2 is disabled it is necessary to globally clean it to ensure any data written that is stored in the L2 cache is cleaned out.

Finally, it is important that this code is mapped 1:1 with physical memory, because during the execution of this code, the MMU turns off and when the virtual address location, the code was executing from is not the same as the physical address, unpredictable results occur when the instructions are fetched. The CPWAIT macro at the end of the sequence ensures that any code after the macro, sees the effects of the MMU being disabled.

#### Example 7. Disable the MMU

```

@ This code disables the MMu. It is important that the L1 data cache

@ be cleaned and disabled before the MMU is disabled.

mrc p15, 0, r0, c1, c0, 0 @ Read the ARM control register

bic r0, r0, #0x1

mcr p15, 0, r0, c1, c0, 0 @ Disable the MMU

CPWAIT r0

```

July 2007

Order Number: 315058-001US

# 3.1.1 Translation Look Aside Buffers (TLB)

In order to increase the speed of memory address translations, the 3rd generation microarchitecture implements two fully associative 32-entry translation look aside buffers (TLBs).

- One is used to cache the lookup of instruction address translations

- The other is for data address translations

When an address translation occurs, the appropriate TLB (instruction or data) is checked prior to performing a 'table walk' to the page table residing in the backing levels of memory. When a cached page table entry is found in the TLB, the address translation, as well as permission and cacheability checks, occur based on the information cached in the TLB. Because the TLB is used to cache page table entries for use by the MMU, the TLB only operates when the MMU is enabled. Some operations, such as TLB entry locking, require that the MMU be enabled or unpredictable results occur.

When an entry is not found in the TLB, a 'table-walk' occurs to load the page table entry from the backing levels of memory. Page table entries are cached in the L2 cache, depending on configuration of certain control bits in the Translation Table Base Register. When table walks are configured to be cacheable in the L2, the L2 cache is checked next. When the table walk does not hit in the L2 cache, then a memory access occurs to the external memory.

Example 8 sets the base address of the page table in main memory. When the MMU does not find a page table entry in the TLB, it uses the Translation Table Base Register (TTBASE) to calculate the physical address where it reads the page table entry. Changing page table base from one page table to another likely affects the mappings or cacheability of certain areas of memory, so it is important that the L1 caches and BTB are empty when the mappings are changed. When a line was valid in the cache and its virtual address changed or became no longer cacheable, unpredictable results occur.

#### Example 8. Changing the Page Table Base

```

@ This code sets the page table base register. The address in this register

@ defines the base address that are accessed when a 'table walk' is

@ performed.

TTBR OC, 0x18

@ Page table entries are outer cacheable

.set

NOTE: ICache, DCache, and the BTB need to all be cleaned/invalidated before

@

this point, to ensure any data which resides in memory

locations that are affected by new mappings is not cached in any way.

@

When any updates to the page table about to be used have just been made,

@

It is necessary to also invoke a DWB operation.

ldr r1, =page_table base

orr r1, r1, #TTBR_OC

@ Allow table walks to be L2 cacheable

mcr p15, 0, r1, c2, c0, 0

@ Write the page table base

@ Globally invalidate I, D TLB

mcr p15, 0, r0, c8, c7, 0

```

After the page table base has changed, both the instruction and data TLBs are invalidated, because these contain cached page table entries from the old page table, and any accesses to those entries produce a 'hit' without correctly checking the values in memory. Finally, a CPWAIT macro is used to ensure that any code executing after this code sequence sees the new mappings.

When page table entries are being modified by software, it is also important that similar steps be taken to ensure stale data is not cached anywhere within the 3rd generation microarchitecture. It is necessary to invalidate both the instruction and data TLBs, in case any of the entries being modified had previously been cached in the TLBs.

It is also necessary to clean and invalidate lines in the L1 data cache that exist due to the memory accesses to the page table entries. In particular stores to the page table must be properly forced out to memory. Once the TLB has been invalidated and the L1 data cache has been cleaned and invalidated, the next memory access to the virtual address, whose translation was modified, results in a table walk which accesses the updated information.

The entries for the address space containing the code executing the change in the page table base must not have its mappings changed while it is executing. When the mapping changes, memory accesses (such as those fetching future instructions into the pipeline) cause entries to be created in the instruction TLB after it has been invalidated, but before the effect of the page table change was observed. When the virtual to physical address translation of those entries was changing between the two sets of page tables, then the old ones become cached after this code had completed.

#### Example 9. Incrementally Locking Instruction TLB Entries

```

.align 6

@ r0, r1 and r2 contain the virtual addresses to translate and lock into

@ the instruction TLB. The TLB entries specified by r0, r1, and r2 must

@ not already be locked in the ITLB.

@ Hardware ensures that accesses to CP15 occur in program order

mcr p15,0,r0,c8,c5,1

@ Invalidate ITLB Entry specified in r0.

mcr p15,0,r1,c8,c5,1

@ Invalidate ITLB Entry specified in r1.

mcr p15,0,r2,c8,c5,1

@ Invalidate ITLB Entry specified in r2.

mcr p15,0,r0,c10,c4,0

@ Translate virtual address (r0) and lock into

@ instruction TLB

mcr p15,0,r1,c10,c4,0

@ Translate virtual address (r1) and lock

@ into instruction TLB

@ Translate virtual address (r2) and lock into

mcr p15,0,r2,c10,c4,0

@ instruction TLB

CPWATT r0

@ The MMU is ensured to be updated at this point; the next instruction

@ sees the locked instruction TLB entries.

```

At times it is desirable to lock entries in the TLB to improve performance. When an entry is locked in the TLB it is never evicted and always produces a 'hit' when the virtual address is translated. When a translation is cached in the TLB it is not necessary for the MMU to execute a 'table walk', which creates a delay while it retrieves the information from the L2 cache or even main memory.

Note:

When locking an entry into the TLB, when the virtual address being translated were already in the TLB and valid, then issuing a lock operation on that address, produces unpredictable results.

For this reason, it is necessary to ensure that the address is not valid in the TLB first, either by globally invalidating the TLB or by specifically invalidating the virtual addresses which are about to be locked. Also due to this restriction, take care that the code executing the lock is not in the same page (referenced through the same TLB entry) as the address being locked. There is the possibility that the very end of this code sequence occurs on a page boundary, and the instructions after the code sequence then occurs on a new page (and therefore a new TLB entry). When the TLB entry being locked was the next entry after the code, it is already in the TLB when the lock occurs, due to fetching and speculative execution of the instructions after the CPWAIT.

Note:

An alignment directive is used to ensure the code sequence does not cross a page boundary to prevent a table walk from the above scenario.

Since this is an example of 'incremental' TLB locking, where system software repeatedly calls this function to lock different entries each time, the specific entry invalidate operation is used. This ensures that the entry being locked is not present in the TLB when the lock operation is performed. It is important that the entries being invalidated are not locked in the TLB, were these then invalidated by MVA operation have unpredictable results. Because there is no method to query the TLB for which entries it has locked, it is necessary to store this information elsewhere in order to check when an entry was already locked in the TLB. For this reason, it is recommended that the system software maintain a table of locked entries.

Only 31 entries in the TLB are lockable. Attempting to lock the 32nd way fails and the request to lock that entry is ignored.

July 2007

Order Number: 315058-001US

## **Example 10. Invalidating and Locking Data TLB Entries**

```

@ r1, and r2 contain the virtual addresses to translate

@ and lock into the data TLB

mcr p15,0,r1,c8,c6,1

@ Invalidate the data TLB entry specified by the

@ virtual address in r1

mcr p15,0,r1,c10,c8,0

@ Translate virtual address (r1) and lock into

@ data TLB

@ Repeat sequence for virtual address in r2

mcr p15,0,r2,c8,c6,1

\ensuremath{\text{@}} Invalidate the data TLB entry specified by the

@ virtual address in r2

mcr p15,0,r2,c10,c8,0

@ Translate virtual address (r2) and lock into

@ data TLB

CPWAIT r2

@ wait for locks to complete

@ The MMU is ensured to be updated at this point; the next instruction

@ sees the locked data TLB entries.

```

This code sequence illustrates how to lock page table entries in the data TLB. The instruction is virtually identical to the instruction TLB locking sequence, except that CRm=8 instead of 4. For this example, the specific addresses being locked are first invalidated in the data TLB. This is a way of avoiding the previously mentioned problem where locking an address in the TLB that is already valid in the TLB causes unpredictable results. When the lines being invalidated were not in the TLB, then the invalidation instruction acts like a no-op and has no results. It is still necessary to ensure that any of the entries being locked have not already been locked into the TLB. For this reason it is still necessary to maintain a separate table of locked TLB entries.

In the following examples, both the instruction and data TLB instructions are shown together in the same code sequences. Both operations are nearly identical, and both have the same effect on respective TLBs. The only difference between these, is the CRm field of the co-processor access instruction.

#### **Example 11. Invalidating TLB entries**

```

@ This code invalidates a specifc entry in the TLB. The entry invalidated

@ corresponds to the virtual address specified in r0.

@ To invalidate in the iTLB, CRm=5. To invalide in the dTLB, CRm=6

mcr p15, 0, r0, c8, c5, 1

@ Invalidate addr in r0 in instruction TLB

mcr p15, 0, r0, c8, c6, 1

@ Invalidate addr in r0 in data TLB

```

The instructions above invalidate specific lines in either the instruction or data TLBs depending on which co-processor access instruction is issued. This operation was used in the previous examples just before locking, in order to ensure that the entry is not valid and unlocked in the TLB. Note, that when the entries being invalidated are in the TLB and are locked, the result is unpredictable. It is important for this reason to first globally unlock the TLB or use a table of locked entries to check when it has already been locked.

July 2007

Order Number: 315058-001US

#### Example 12. Globally Invalidating the TLBs

```

mov r0, #0 @ The data in R0 is to be zero

@ This code globally invalidates both the instruction and data TLBs

@ The data in r0 is ignored.

mcr p15, 0, r0, c8, c7, 0 @ Globally invalidate I, D TLB

```

Both the instruction and data TLBs are globally invalidated by writing to co-processor 15, register 8. The operation simultaneously ensures that no valid lines are left in either the data or instruction TLBs. However, when any TLB entries locked before this operation, are not invalidated, remain locked with contents unchanged. In order to ensure that the global invalidate operation leaves no valid entries in either TLB, it is necessary to issue a global unlock on each TLB before invalidating.

### Example 13. Globally unlocking the TLB

```

This code globally unlocks the instruction and data TLBs. When any entries are valid and locked in the targeted TLB when this code executes, these become unlocked and remain unchanged.

To globally unlock the iTLB, CRm=4. To globally unlock the dTLB, CRm=8.

mov r0, #0

@ The data in R0 is to be zero mcr p15, 0, r0, c10, c4, 1

@ Globally unlock instruction TLB mcr p15, 0, r0, c10, c8, 1

@ Globally unlock data TLB

```

This example shows how to globally unlock all entries in both the instruction or data TLB. This is performed by writing to the co-processor 15 register with CRm=4 for the iTLB and CRm=8 for the dTLB. Since it is required that entries in the TLB are unlocked before these are invalidated, it is useful to globally unlock the TLB to be certain that no locked entries exist. Then the TLB is invalidated (either globally or via specific addresses) without the possibility of a locked entry having an invalidate instruction issued against it.

#### 3.2 Cache Management

The 3rd generation microarchitecture contains 32 KB of L1 data cache, 32 KB of L1 instruction cache, and 0 KB, 256 KB, or 512 KB of L2 cache. All microarchitecture cache management operations are performed by utilizing co-processor 15, register 7 (cache functions), register 9 (cache lock down), and register 1 (control). Operations are typically "global", meaning one instruction has an effect on the entire cache, or are "per-line", meaning each cache control instruction has an effect on a single cache line. In the case of "per-line" instructions, the line is specified either using a modified virtual address or by a set and way index.

Some of the examples in this section contain references to a CPWAIT macro. This macro is used as a way to delay execution of subsequent code until the previous co-processor 15 operation has taken effect, refer to Section 2, "CPWAIT Macro" on page 11 for more information.

The caches on the 3rd generation microarchitecture help to isolate its execution from the latency of accessed memory and buses. The microarchitecture attempts to access the L1 or L2 cache, in lieu of sending a memory operation all the way out to memory, and this reduces the number of cycles a memory operation instruction must wait before it is retired. In order for some memory and device access routines to function correctly however, certain memory regions and certain explicit memory operation ordering must occur some of the time. The code sequences in this section are reference examples that explain how system software controls the cache, allowing some control over how and when memory operations are observed outside the microarchitecture.

Because cache sizes are different depending on the ASSP, it is necessary to check the size at run-time in order to allow the software to be portable. The co-processor 15 ARM cache type registers contain information about both the L1 and L2 caches.

#### 3.2.1 L1 Cache

The 3rd generation microarchitecture L1 cache consists of separate 32 KB 4-way set associative instruction and data caches. When a region of memory is marked cacheable in the L1, a fetch of either instruction or data memory cause a cache line allocation and fill. When a subsequent instruction fetch occurs, when the data is in the L1 cache and the line is valid, the instruction from the cache line is used and no external memory operation occurs. The operations described in this section allow system software to explicitly cache, clean, invalidate, lock, and unlock lines in the L1 instruction and data caches.

It is important to note that the operation of the L1 and L2 caches in the 3rd generation microarchitecture is closely linked to the operation of the MMU, the TLB, and the BTB. More information on these components are found in the following sections: "Virtual Memory (MMU)" on page 16, "Translation Look Aside Buffers (TLB)" on page 20, and "Branch Target Buffer (BTB)" on page 47.

#### 3.2.1.1 L1 Instruction Cache Enable/Disable

The 3rd generation microarchitecture L1 instruction cache is enabled independently from the MMU or BTB. When the L1 instruction cache is enabled, on every instruction fetch that is found to be cacheable by the MMU (or every fetch when the MMU is disabled), the instruction cache are checked and when the instructions are found there these are used. When the address is not found in the L1 instruction cache, a fill request is issued and a new cache line is allocated to contain the instruction data from memory. Although these operations refer to 'enabling' and 'disabling' the L1 instruction cache, it is better to view these operations as merely enabling and disabling the ability of the L1 instruction cache to fill a cache line.

In other words, with the exception of a new line being allocated and filled in the L1 instruction cache, every aspect of the L1 instruction cache remains active all of the time. This means that when a cacheable instruction fetch occurs, the L1 instruction cache in the 3rd generation microarchitecture is checked prior to any access to external memory. When the system software elects to ensure that the L1 instruction cache is never 'hit', it is necessary to both disable its ability to allocate and fill new lines, and to invalidate all the lines which already exist in the L1 cache. When completely invalidated and unable to fill new lines, the L1 instruction cache is effectively disabled.

Note:

This behavior (hitting the cache when it is disabled) is deprecated on the 3rd generation microarchitecture. It is possible this behavior changes on future generations so do not let software depend it its existence.

#### Example 14. Enable the L1 Instruction Cache

```

@ Enable I-cache

mrc p15, 0, r3, c1, c0, 0 @ Get control register

orr r3, r3, #0x1000

@ Set I bit (bit 12)

mcr p15, 0, r3, c1, c0, 0 @ Update control register

```

The code above enables the L1 instruction cache on the 3rd generation microarchitecture. This is done by reading Register 1 of the Control Register and modifying it so bit 12 (L1 I-Cache Enable/Disable) is turned on. Unlike the L1 data cache, the L1 instruction cache on the microarchitecture is enabled at any time, independently of the MMU or BTB. However, it is important to note that the behavior of the L1 instruction cache is very different with respect to the MMU being enabled or disabled. When the MMU is disabled and the L1 I-cache is enabled, every instruction fetch, regardless of address, is cached. When the MMU is enabled and the L1 I-cache is enabled, whether or not instructions are cached depends on the cacheable bit being set on the page corresponding to the instruction memory address being fetched. Also when the MMU is off, no address translation takes place. Therefore the addresses in the L1 instruction cache when the MMU is off are physical addresses.

#### Example 15. Disable the L1 Instruction Cache

```

@ Disable I-cache

mcr p15, 0, r3, c1, c0, 0 @ Undate combo

@ Get control register

@ Update control register

Now that I-cache is disabled, it is necessary to invalidate

@ the L1 I-Cache and the BTB as described in the text.

```

The L1 instruction cache on the 3rd generation microarchitecture is disabled by reading Register 1 of the Control Register and modifying it so bit 12 (L1 I-Cache Enable/Disable) is cleared. After this operation, even though the instruction cache is disabled, any lines that are not invalid cause a hit when memory address is fetched. When this is not the desired behavior, it is the responsibility of system software to invalidate the L1 instruction cache as well as the BTB, in order to ensure future instruction fetches do not hit the L1 cache. Operations on the L1 cache, such as invalidation and unlocking, work with the cache enabled or disabled. The reason the L1 instruction cache is invalidated after it is disabled, rather than before, is to avoid caching the code that does the disabling (and any instructions also in the lines it occupies), which results in the code being 'trapped' in the L1 instruction cache after the cache becomes disabled.

## 3.2.2 L1 Instruction Cache Operations

This section describes various operations that have an effect on L1 instruction cache lines, including locking, unlocking and invalidating on a per-line and global basis.

It is desirable to lock certain L1 instruction cache code routines. This favors achieving higher performance on code often executed, such as interrupt handler routines. When instructions are locked in the L1 instruction cache, these are always available and always produce a cache 'hit' every time the memory location is executed.

#### Example 16. Lock Lines In the L1 Instruction Cache

```

@ This code locks the "lockMe" routine

codeLock:

ldr r0, =(lockMe)

@ ptr to first cache line to lock

bic r0, r0, #0x1F

ldr r1, =(lockMeEnd) @ ptr to last cache line to lock

@ up to last instruction of function

sub r1, r1, #1

bic r1, r1, #0x1F

lockLoop:

mcr p15, 0, r0, c7, c5, 1 @ invalidate IC Line first

mcr p15, 0, r0, c9, c5, 0 @ lock next line into Icache

cmp r0, r1

@ check when done

add r0, r0, #32

@ increment by cache line size

bne lockLoop

@ when not done, do next line

b finished

nop

nop

nop

nop

@ Align the function on a cache-line boundary

.p2align 5

lockMe:

@ This is the code to lock into I-cache

mov r1, #5

add r1, r1, #8

mov pc, lr

@...

lockMeEnd:

```

The previous code sequence locks an L1 instruction cach function. It accomplishes this by calculating the cache line - aligned start and end address of a function, then looping through each cache line the function occupies, locking the line. The line lock operation is performed by writing the modified virtual address to co-processor 15, register 9. It is important that no part of the code being locked is already present in the L1 instruction cache before this operation is executed.

When an address being locked is already in the instruction cache, the operation fails and the line is not locked. For this reason, each line in the instruction cache is invalidated before it is locked, to avoid this possibility. Due to the fact that way0 of each set cannot be locked, a maximum of 24 KB of code is locked in the L1 instruction cache. However, in practice the maximum is less, due to the limitation that only 3 ways of each set are locked at a time.

In general, it is useful for system software to maintain a table of locked lines. Since there is no method for determining how 'full' the instruction cache is with locked lines, it is necessary to check a separate table, in order to determine when a line lock operation is successful. Because fetches for speculative execution cause instructions after the end of the lock loop to be fetched into the instruction cache, it is possible in the case where the code being locked is part of the next cache line, that the last line lock fails because the line is already in the cache.

For this reason, enough NOPs to fill the pipeline are inserted after the loop, so these are fetched instead of the code after the end of the loop. The function occurring next is aligned on a cache line boundary, so it is ensured it does not occupy the same cache lines as the function performing the lock.

#### Example 17. Globally Unlock the L1 Instruction Cache

```

mov r1, #0

@ The data in R1 is to be zero

mcr p15, 0, r1, c9, c5, 1 @ unlock all lines in the L1 I-cache

@ data in R1 is ignored

```

The code above globally unlocks the L1 instruction cache. This operation does not modify or invalidate any contents of the valid lines in the instruction cache. After this operation is complete, no lines are locked, and these are potentially evicted when an instruction fetch occurred. The L1 instruction cache is unlocked by performing a write to co-processor 15, register 9. The contents of the data written are ignored. This operation is performed and has the same effect with the L1 instruction cache enabled or disabled.

It is necessary to invalidate instructions in the L1 cache when these have been modified externally and the modification needs to have taken effect the next time the 3rd generation microarchitecture executes those instructions. When L1 instruction cache lines are invalidated, it ensures that the next time an instruction fetch to that memory address occurs, the data is retrieved externally from the L1 cache.

#### **Example 18. Unlock and Invalidate L1 Instruction Cache Lines**

```

@ This code unlocks & validates a memory region in the 11 I-cache.

@ r0 contains the MVA of the address to start the unlocking

@ r1 contains the number of 32-byte lines to invalidate & unlock.

@ In this example, 16 lines are unlocked and invalidated.

mov r1, #16

unlockLoop:

mcr p15, 0, r0, c7, c5, 1 @ invalidate and unlock address R0 in I-cache

add r0, r0, #32

@ increment by cache line size

subs r1, r1, #1

@ decrement loop counter, set flags

bne unlockLoop

@ when not done, do next line

```

This example invalidates cache lines in the L1 instruction cache. The number of lines specified in register r1 are invalidated sequentially, starting at the line that corresponds to the modified virtual address stored in register r0. This is done by incrementing a pointer by the size of a line and writing the address to co-processor 15, register 7. When the cache does not contain a valid entry corresponding to the modified virtual address, no action is taken.

Before the invalidation takes place, this operation also unlocks the line when it is locked. For this reason, the invalidate operation is used as a way to unlock only certain routines in the L1 instruction cache, without having to unlock all of thesewith a global unlock.

July 2007

Order Number: 315058-001US

It is important to be aware that the BTB also contains information relating to instructions. When routines are invalidated in the L1 instruction cache, any corresponding branch entries in the BTB are not invalidated. When the purpose of the operation is to allow the 3rd generation microarchitecture to execute code that has been modified in memory, then it is also necessary to invalidate the BTB, to ensure the new code when fetched has the correct entries in the BTB. When the BTB and the L1 instruction cache are not in sync, then the results are unpredictable.

#### Example 19. Globally Invalidate the L1 Instruction Cache

```

mov r1, #0 @ The data in R0 is to be zero

mcr p15, 0, r1, c7, c5, 0 @ Invalidate the I-cache and BTB

@ Data in r1 is ignored

```

The code above performs a global invalidation of the L1 instruction cache. It does this by performing a write to co-processor 15, register 7, the contents of the register written are ignored. Note, that when any lines in the L1 instruction cache are locked, these are not touched and remain valid, and locked after this operation. When ensured global invalidation is the desired behavior, and when there is the possibility of locked lines existing in the cache, then the cache lines must be unlocked either through a global unlock operation, or by virtual address before the global invalidate.

This operation is used as part of the sequence to disable operation of the 3rd generation microarchitecture L1 instruction cache, by first disabling the cache and second ensuring all lines are invalidated. Also note, that since the BTB also contains branch prediction data, it is implicitly invalidated as well to prevent stale branch data from causing unpredictable behavior.

#### 3.2.3 L1 Data Cache Enable/Disable

The 3rd generation microarchitecture L1 data cache is dependent on the MMU. In order for it to be enabled, the MMU must have been enabled first. The MMU performs the address translation lookup, and determines when the data being accessed is cacheable in the L1 data cache. When the address being accessed is determined to be cacheable, then the L1 data cache allocates a line and fills it with data from the address being accessed on a read.

For writes, when a valid cache line already exists, the 3rd generation microarchitecture L1 Data cache is configured to write only to the cache line (write-back), or write to the cache line as well as out to external memory (write-through). This behavior is determined by the page table entry bits corresponding to the memory address being accessed.

#### Example 20. Enable the L1 Data Cache

```

@ MMU must be enabled

@ Enable dcache

mrc p15, 0, r3, c1, c0, 0 @ Get Control Register

orr r3, r3, #0x0004

@ Set C Bit (bit 2)

mcr p15, 0, r3, c1, c0, 0 @ Update control register

```

This routine enables the L1 data cache in the 3rd generation microarchitecture. This is accomplished by reading, modifying, and writing bit 2 (L1 D-Cache enable/disable) in co-processor 15 register 1. Note, that the MMU must be enabled prior to or at the same time as the enabling of the L1 data cache. This requirement is different than the L1 instruction cache, which does not require the MMU to be enabled in order to operate. When this routine is executed without the MMU being enabled, the results are unpredictable. When the L1 data cache is enabled, memory pages that are marked as cachable allow a cache 'hit' when the data these contain is already in the cache, and memory pages marked as write-back is cached on write hits.

# Example 21. Disable the L1 Data Cache

```

@ Disable dcache

mrc p15, 0, r3, c1, c0, 0 @ Get Control Register

bic r3, r3, #0x0004

@ Clear C Bit (bit 2)

mcr p15, 0, r3, c1, c0, 0 @ Update control register

@ Now unlock, clean, and invalidate L1 D-cache

```

This code disables the L1 data cache in the 3rd generation microarchitecture. This is accomplished by reading, modifying, and writing bit 2 (L1 D-Cache enable/disable) in co-processor 15 register 1. Note, that even though the L1 data cache is disabled after this operation completes, any valid lines in the cache results in both cache hits on reads for regions marked cacheable, as well as writes for memory regions marked write-back. This behavior is unlikely to be desired because any changes to memory in the regions that are in the cache are not observable to the processor, and any writes to regions in the cache are written into the cache, but never cleaned out. For this reason, it is necessary to unlock, clean, and invalidate all L1 data cache lines. Because invalidate, clean, and unlock operations still affect the cache, even though it is disabled, this is done after the L1 data cache is disabled, to ensure no new lines are allocated during this operation or afterwards.

July 2007

Order Number: 315058-001US

# 3.2.4 L1 Data Cache Operations

This section describes various operations that are performed on the L1 data cache. These operations change the behavior of regions of the data cache, as well as assist in turning it on or off. Lines in the data cache are locked, cleaned (written out when dirty), and invalidated, either globally or on a per line basis. Regions of the L1 data cache are used to permanently hold and cache a small part of memory, or these are configured to act as a small amount of high-speed "scratch memory", that is not present in allocated system memory. Specific regions of locked data memory are cleaned, but still remain locked in cache, in order to have the contents written out to main memory in a cache-line burst operation, even though these are written in small amounts multiple times.

## Example 22. Lock Lines in the L1 Data Cache (Sheet 1 of 2)

```

@ Restrictions:

@ Prefetch abort handler MUST turn off lock mode bit

@ as soon as possible.

@ Data abort handler MUST turn off lock mode bit as

@ soon as possible.

@ When there are any imprecise aborts during locking

@ the result of locking is unpredictable.

@ NOTE: This routine always locks at least one line.

@

End address needs to be greater than start address.

@ PSR bit defines

.setPSR_I, 0x80

.setPSR_F, 0x40

@ LockDCache flags

.setL_LEN, 0x01

.setL INV, 0x02

@ Data Cache Lock Mode

.setM LOCKED, 0x01

.setM_NOT_LOCKED, 0x00

@ Cache Line Size

.setLINE SIZE, 0x20

@ _LockDCache(Start,End_or_Length,Flags)

@

@ Inputs

@ R0 Start Address

R1 End Address (inclusive) or Length

R2 Flags

@ Outputs

@ RO Success (1) / Failure (0)

@ Registers used

@ R1 - R3, IP

@

@ Usage:

@

@ When a region length is specified in R1 then the

@ L LEN flag must be set. All data cache

@ unlocked and invalidated when the L_INV flag is set.

@ When several things are to be locked into the cache

@ the L INV flag needs to be set for the first item

@ to be locked and clear for subsequent items.

```

July 2007 Software Design Guide

Order Number: 315058-001US 3rd Generation Intel XScale® Microarchitecture

Software Design Guide

July 2007

Order Number: 315058-001US

### Example 22. Lock Lines in the L1 Data Cache (Sheet 2 of 2)

```

.p2align 2

.global LockDCache

.type LockDCache, function

LockDCache:

mrs ip, cpsr@ Save CPSR

orr r3, ip, #PSR_I | PSR F

msr cpsr c, r3@ Disable Interrupts

mrc p15, 0, r3, 1, 0, 0

mcr p15, 0, r3, 1, 0, 0@ Force a DCU drain

tst r2, #L INV

mcrnep15, 0, r0, c9, c6, 1@ Unlock D-Cache

mcrnep15, 0, r0, c7, c6, 0@ Invalidate D-Cache

mov r3, #M LOCKED

mcr p15, 0, r3, c9, c6, 0@ Set Lock Mode

tst r2, #L LEN

addner1, r1, r0

subner1, r1, #1

CacheFill:

ldr r2, [r0], #LINE SIZE

mrc p15, 0, r3, 1, 0, 0

mcr p15, 0, r3, 1, 0, 0@ Force a DCU drain

cmp r0, r1

ldrlsr3, [r0], #LINE_SIZE

mrclsp15, 0, r3, 1, 0, 0

mcrlsp15, 0, r3, 1, 0, 0@ Force a DCU drain

cmplsr0, r1

bls CacheFill

orr r2, r2, r3@ Create a dependency stall

mrc p15, 0, r0, c9, c6, 0@ Read Lock Mode

mov r2, #M NOT LOCKED

mcr p15, 0, r2, c9, c6, 0@ Clear Lock Mode

msr cpsr f, ip@ Reset Interrupt flags

and r0, r0, #M LOCKED@ Test lock flag

mov pc, lr

.Lfe1:

.size LockDCache, .Lfe1- LockDCache

```

The above routine in Example 22 locks lines of data from memory into the L1 data cache. This is useful as a high-performance method for accessing periodically used symbols or lookup tables in close proximity in memory. Because of the fact that way0 of the data cache cannot be locked, a maximum of 24 KB of L1 data cache is locked. In practice, the maximum is less than that, depending on the addresses of the locked lines and due to the fact that at most 3 ways of each set are locked. The locking is accomplished by putting the L1 data cache in 'lock mode' by writing a '1' to co-processor 15 register 9. Once the data cache is in 'lock mode', any newly allocated cache lines have the lock bit set, which prevents these from being evicted. The routine puts the data cache in lock mode, then proceeds to load the first word of each cache line using a 'ldr' instruction. The data being loaded into register 'r2' or 'r3' is thrown away, since the 'ldr' instruction is used just to cause the line to be fetched and locked. Loading the first word causes the 3rd generation microarchitecture to fetch the full 32-bytes to fill each cache line.

Note:

This routine takes advantage of a special 3rd generation microarchitecture feature writing the Control Register has the side effect of forcing a Data Cache Unit (DCU) drain. Do not depend on this behavior in other microarchitectures!

It is important to note that when any part of the data being fetched already existed in the L1 data cache, the data is not fetched into the cache, and the lock operation for that cache line does not occur. To avoid this, the code above has a flag that unlocks and invalidate all data in the cache before locking any new data.

Note:

Any existing data is lost so the cache needs to be cleaned before the lock routine is called in this case.

Additionally, care must be taken to ensure the processor is not interrupted during this operation. When the lock mode is on, any memory operation resulting in a data cache fill causes that line to be locked, and were an interrupt handler to execute during this time, undesired results occur. It is recommended that interrupts be disabled when performing this operation. For more information on interrupts in the 3rd generation microarchitecture, see "Disable Interrupts" on page 62, and "Enable Interrupts" on page 62.

#### Example 23. Create L1 Data Cache RAM

```

@ R1 contains the virtual address of a region of memory to configure as data RAM,

@ which is aligned on a 32-byte boundary.

@ MMU is configured so that the memory region is cacheable.

@ RO is the number of 32-byte lines to designate as data RAM. In this example 16

@ lines of the data cache are re-configured as data RAM.

@ MMU and data cache are enabled prior to this code.

@ Care must be taken to ensure no interrupts occur during the time 'lock mode'

@ is enabled. It is recommended interrupts be disabled during this operation.

.macro ALLOCATE, Rx

mcr p15, 0, \Rx, c7, c2, 5

.endm

.macro BARRIER, Rd

mcr p15, 0, \Rd, c7, c10, 5 @ DMB Operation to provide memory barrier

@ contents of \Rd ignored

.endm

BARRIER r0

mov r2, #0x1

mcr p15, 0, r2, c9, c6, 0 @ Put the data cache in lock mode

CPWAIT r3

mov r0, #16

LOOP1:

ALLOCATE r1

@ Allocate and lock a tag into the data cache at

@ address [R1].

@ Note that newly allocated line contains unpredictable data.

@ The caller to this function ensures it writes the line with known

@ data to avoid using the unpredictable data.

add r1, r1, #32

@ Increment to the next line

subs r0, r0, #1

bne LOOP1

@ Turn off data cache locking

mov r2, \#0x0

mcr p15, 0, r2, c9, c6, 0 @ Take the data cache out of lock mode.

CPWAIT r3

```

July 2007

Order Number: 315058-001US

This example creates "data cache RAM" by locking lines that correspond to an unallocated memory region in L1 data cache. This is useful when a high-performance scratch pad region is required, either to use as a place to store values that do not fit in the available registers, or as a place to consolidate and quickly access symbols which are widely dispersed in physical memory.

Because way0 of the L1 data cache cannot be locked, a maximum of 24 KB of L1 data cache is locked. The actual number of lines is less than that, due to the fact that only 3 ways of each set are locked.