# Synchronization CS 418 Lecture 23

### **Topics**

- · Locks

- Barriers

- · Hardware primitives

# Types of Synchronization

### Mutual Exclusion

· Locks

### **Event Synchronization**

- · Global or group-based (barriers)

- · Point-to-point

- CS 418 5'04 =

# Busy Waiting vs. Blocking

### Busy-waiting is preferable when:

- · scheduling overhead is larger than expected wait time

- · processor resources are not needed for other tasks

- schedule-based blocking is inappropriate (e.g., in OS kernel)

- 3 - C5 418 5'04

# A Simple Lock

```

lock: ld register, location

cmp register, #0

bnz lock

st location, #1

ret

unlock: st location, #0

ret

```

# Need Atomic Primitive!

Test&Set

Swap

Fetch&Op

· Fetch&Incr, Fetch&Decr

Compare&Swap

- 5 - CS 418 S'04 -

# Test&Set based lock

```

lock: t&s register, location

bnz lock

ret

unlock: st location, #0

ret

```

CS 418 S'04

# T&S Lock Performance

```

Code: lock; delay(c); unlock;

Same total no. of lock calls as p increases; measure time per transfer

```

# Test and Test and Set

```

A: while (lock != free);

if (test&set(lock) == free) {

critical section;

}

else goto A;

```

- (+) spinning happens in cache

- (-) can still generate a lot of traffic when many processors go to do test&set

CS 418 S'04

### Test and Set with Backoff

### Upon failure, delay for a while before retrying

· either constant delay or exponential backoff

#### Tradeoffs:

- (+) much less network traffic

- (-) exponential backoff can cause starvation for highcontention locks

- new requestors back off for shorter times

But exponential found to work best in practice

.9-

CS 418 5'04 ---

# Ticket Lock (fetch&incr based)

#### Two counters:

- next\_ticket (number of requestors)

- now\_serving (number of releases that have happened)

### Algorithm:

- First do a fetchåincr on next\_ticket (not teståset)

- When release happens, poll the value of now\_serving

- -if my\_ticket, then I win

Use delay; but how much?

11 - \_\_\_\_\_\_ CS 418 S'04

# Test and Set with Update

Test and Set sends updates to processors that cache the lock

#### Tradeoffs:

- (+) good for bus-based machines

- (-) still lots of traffic on distributed networks

Main problem with teståset-based schemes is that a lock release causes all waiters to try to get the lock, using a teståset to try to get it.

- 10 -

= CS 418 5'04

# Ticket Lock Tradeoffs

- (+) guaranteed FIFO order; no starvation possible

- (+) latency can be low if fetch&incr is cacheable

- (+) traffic can be quite low

- (-) but traffic is not guaranteed to be O(1) per lock acquire

- 12

= CS 418 5'04

# Array-Based Queueing Locks

Every process spins on a unique location, rather than on a single now\_serving counter

fetch&incr gives a process the address on which to spin

#### Tradeoffs:

- (+) guarantees FIFO order (like ticket lock)

- (+) O(1) traffic with coherence caches (unlike ticket lock)

- (-) requires space per lock proportional to P

- 13 - CS 418 S'04 =

### guarantee

software

Tradeoffs:

- (+) less storage than array-based locks

- (+) O(1) traffic even without coherent caches

- (-) compare&swap not easy to implement

CS 418 S'04

List-Base Queueing Locks (MCS)

All other good things + O(1) traffic even

Uses compare&swap to build linked lists in

Locally-allocated flag per list node to spin on

Can work with fetchastore, but loses FIFO

without coherent caches (spin locally)

# Implementing Fetch&Op

#### Load Linked/Store Conditional

= - 16 - =

CS 418 S'04

## Barriers

### We will discuss five barriers:

- · centralized

- · software combining tree

- · dissemination barrier

- · tournament barrier

- · MCS tree-based barrier

CS 418 5'04

# Centralized Barrier

#### Basic idea:

- · notify a single shared counter when you arrive

- · poll that shared location until all have arrived

# Simple implementation require polling/spinning twice:

- · first to ensure that all procs have left previous barrier

- · second to ensure that all procs have arrived at current barrier

Solution to get one spin: sense reversal

- 17 - CS 418 S'04

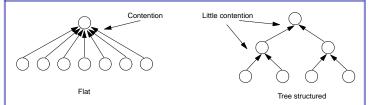

# Software Combining Tree Barrier

Writes into one tree for barrier arrival Reads from another tree to allow procs to continue

Sense reversal to distinguish consecutive barriers

CS 418 S'04

# Dissemination Barrier

log P rounds of synchronization In round k, proc i synchronizes with proc  $(i+2^k)$  mod P

### Advantage:

Can statically allocate flags to avoid remote spinning

- 19 - CS 418 S'04

## Tournament Barrier

Binary combining tree

Representative processor at a node is statically chosen

· no fetch&op needed

In round k, proc  $i=2^k$  sets a flag for proc  $j=i-2^k$

- · / then drops out of tournament and j proceeds in next round

- · / waits for global flag signalling completion of barrier to be set

- -could use combining wakeup tree

- 20 - CS 418 S'04

# MCS Software Barrier

Modifies tournament barrier to allow static allocation in wakeup tree, and to use sense reversal

Every processor is a node in two P-node trees:

- has pointers to its parent building a fanin-4 arrival tree

- has pointers to its children to build a fanout-2 wakeup tree

- 21 - CS 418 S'04

# Space Requirements

### Centralized:

· constant

# MCS, combining tree:

· O(P)

### Dissemination, Tournament:

· O(PlogP)

- 23 - \_\_\_\_\_\_ CS 418 S'04 =

# **Barrier Recommendations**

#### Criteria:

- · length of critical path

- · number of network transactions

- · space requirements

- · atomic operation requirements

CS 418

### **Network Transactions**

### Centralized, combining tree:

- · O(P) if broadcast and coherent caches;

- · unbounded otherwise

### Dissemination:

· O(PlogP)

- 22 -

### Tournament, MCS:

· O(P)

4 - \_\_\_\_\_\_ CS 418 S'04

# Critical Path Length

# If independent parallel network paths available:

· all are O(logP) except centralized, which is O(P)

## Otherwise (e.g., shared bus):

· linear factors dominate

- 25 - CS 418 S'04 =

### **Barrier Recommendations**

### Without broadcast on distributed memory:

- · Dissemination

- MCS is good, only critical path length is about 1.5X longer

- MCS has somewhat better network load and space requirements

# Cache coherence with broadcast (e.g., a bus):

- · MCS with flag wakeup

- centralized is best for modest numbers of processors

### Big advantage of centralized barrier:

· adapts to changing number of processors across barrier calls

- 27 - CS 418 S'04

# Primitives Needed

# Centralized and combining tree:

- · atomic increment

- · atomic decrement

### Others:

- · atomic read

- · atomic write

CS 418 S'04