## 80 core Teraflops Research Processor

## First tera-scale silicon prototype

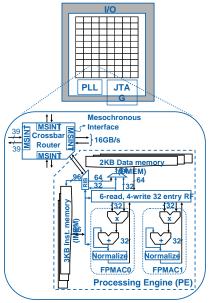

Tiled architecture

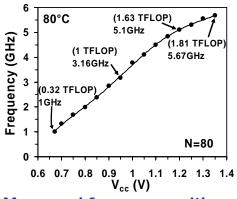

Measured frequency with peak teraflops

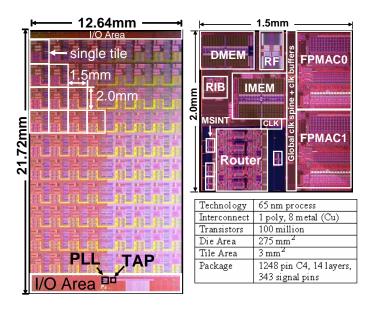

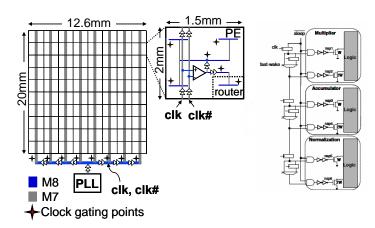

### Chip micrograph and characteristics

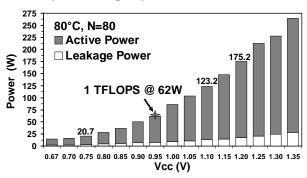

Measured power with peak teraflops

## **Key Features**

- ♦ 80 tiles connected in a 2D mesh

- **♦ Single precision FPMAC cores**

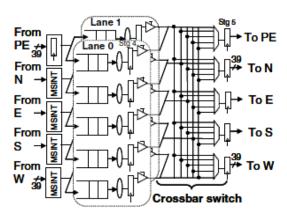

- Non-blocking double-pumped crossbar router w/ 6 ports, 2 VCs

- Dynamic power management

- ♦ 1.01 teraflops @ 0.95V, 62 W

# 80 core Teraflops Research Processor

## First tera-scale silicon prototype

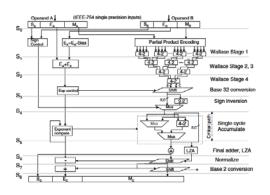

### **Compute Core**

- **★**Single Precision FPMAC engine.

- ♦Fast single-cycle accumulate loop.

### **On-die Interconnect**

- ★ 2-dimensional mesh

- Scalable, reconfigurable, partitionable, power-aware

- ♦ 1.62 Terabits/s bisection BW 75 GB/s aggregate BW

## Power Management

- ★ Mesochronous clocking

- ♦ Scalable, low-power

Dynamic sleep instructions

- ♦ Put FP engine or tile to sleep

- ★ Memory clamping circuits

- ♦ Retain state in arrays in sleep

- ★ Sleep transistors

- ♦ 6x standby leakage reduction

- ★ Voltage and frequency control

FPMAC engine

#### Router

Mesochronous clocking

FPMAC wakeup